# DDR2 SDRAM

**SAA64M4.....- 16 Meg x 4 x 4**

**SAA32M8.....- 8 Meg x 8 x 4**

**SAA16M16.....- 4 Meg x 16 x 4**

For the latest data sheet, please refer to the SpecTek Web site: <http://www.spectek.com>

## Features

- ROHS compliant

- VDD =  $+1.8V \pm 0.1V$ , VDDQ =  $+1.8V \pm 0.1V$

- JEDEC standard 1.8V I/O (SSTL\_18-compatible)

- Differential data strobe (DQS, DQS#) option

- Four-bit prefetch architecture

- DLL to align DQ and DQS transitions with CK

- Four internal banks for concurrent operation

- Programmable CAS Latency (CL): 3 and 4

- Posted CAS additive latency (AL): 0, 1, 2, 3, and 4

- WRITE latency = READ latency -  $1^t_{CK}$

- Programmable burst lengths: 4 or 8

- Adjustable data-output drive strength

- 64ms, 8,192-cycle refresh

- On-die termination (ODT)

## Options<sup>1, 2</sup>

- SpecTek Memory SAA

- Configuration

- 64 Meg x 4 (16 Meg x 4 x 4) 64M4

- 32 Meg x 8 (8 Meg x 8 x 4) 32M8

- 16 Meg x 16 (4 Meg x 16 x 4) 16M16

- Product Code Ux<sup>3</sup>

- Density

- 256 Megabits 6x<sup>3</sup>

- Voltage/Refresh

- 1.8V/8K refresh O8

- Package – Lead-Free

- x4, x8

- 60-ball FBGA (8mm x 12mm) FIF

- x16

- 84-ball FBGA (8mm x 14mm) FPF

- Package – Leaded

- x4, x8

- 60-ball FBGA (8mm x 12mm) FIL

- x16

- 84-ball FBGA (8mm x 14mm) FPL

- Timing – Cycle Time

- 3.0ns @ CL = 5 (DDR2-667) -3

- 3.75ns @ CL = 4 (DDR2-533) -37E

## Designation

| Architecture      | 64 Meg x 4      | 32 Meg x 8    | 16 Meg x 16    |

|-------------------|-----------------|---------------|----------------|

| Configuration     | 16 Meg x 4 x 4  | 8 Meg x 8 x 4 | 4 Meg x 16 x 4 |

| Refresh Count     | 8K              | 8K            | 8K             |

| Row Addressing    | 8K (A0–A12)     | 8K (A0–A12)   | 8K (A0–A12)    |

| Bank Addressing   | 4 (BA0–BA1)     | 4 (BA0–BA1)   | 4 (BA0–BA1)    |

| Column Addressing | 2K (A0–A9, A11) | 1K (A0–A9)    | 512 (A0–A8)    |

**Table 1: Key Timing Parameters**

| Speed Grade | Data Rate (MHz) |        | t <sub>RCD</sub> (ns) | t <sub>RP</sub> (ns) | t <sub>Rc</sub> (ns) |

|-------------|-----------------|--------|-----------------------|----------------------|----------------------|

|             | CL = 4          | CL = 5 |                       |                      |                      |

| -3          | NA              | 667    | 15                    | 15                   | 60                   |

| -37E        | 533             | 533    | 15                    | 15                   | 60                   |

Part Number Example:

**SAA32M8U26AO8FIF-37E**

NOTE: 1. See page 42 for part number options and designations used prior to March 2005.

2. See page 42 for part number options and designations used prior to July 2006.

3. Contact SpecTek Sales for details on availability of the "x" placeholders

## Table of Contents

|                                                                  |    |

|------------------------------------------------------------------|----|

| Features .....                                                   | 1  |

| Options .....                                                    | 1  |

| FBGA Part Marking Decoder .....                                  | 5  |

| General Description .....                                        | 5  |

| Functional Description .....                                     | 10 |

| Absolute Maximum Ratings .....                                   | 12 |

| AC and DC Operating Conditions .....                             | 13 |

| Input Electrical Characteristics and Operating Conditions .....  | 14 |

| Input Slew Rate Derating .....                                   | 17 |

| Data Slew Rating .....                                           | 20 |

| Power and Ground Clamp Characteristics .....                     | 25 |

| AC Overshoot/Ubershoot Specification .....                       | 26 |

| Output Electrical Characteristics and Operating Conditions ..... | 27 |

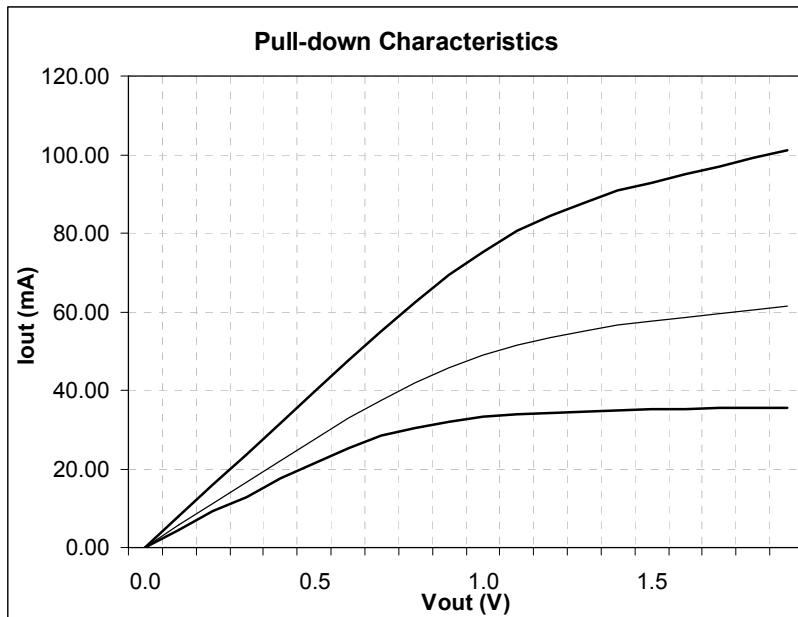

| Full Strength Pull-Down Driver Characteristics .....             | 29 |

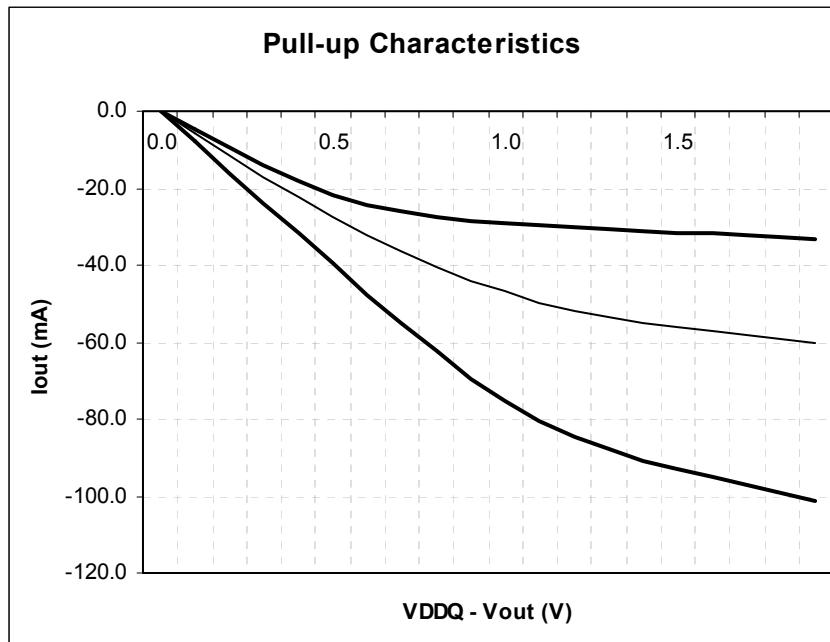

| Full Strength Pull-Up Driver Characteristics .....               | 30 |

| FBGA Package Capacitance .....                                   | 31 |

| IDD Specifications and Conditions .....                          | 32 |

| IDD7 Conditions .....                                            | 34 |

| Notes .....                                                      | 38 |

| Data Sheet Designation .....                                     | 41 |

| Part Number Options and Designations Prior to March 2005 .....   | 42 |

| Part Number Options and Designations Prior to July 2006 .....    | 42 |

| Revision History .....                                           | 43 |

## List of Figures

|            |                                                                           |    |

|------------|---------------------------------------------------------------------------|----|

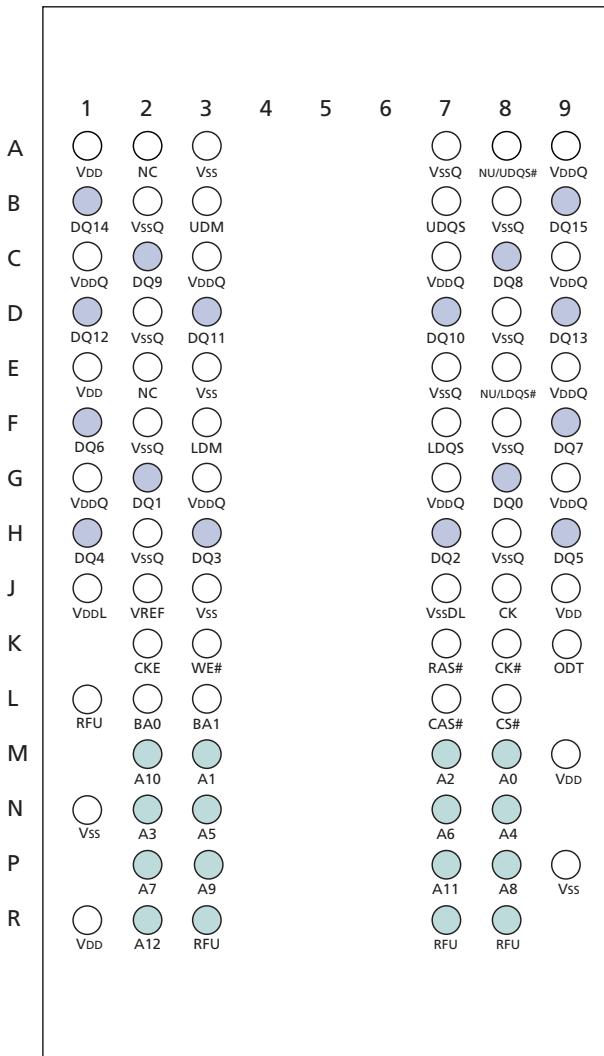

| Figure 1:  | 84-ball FBGA Pin Assignment (x16), 8mm x 14mm (Top View) .....            | 6  |

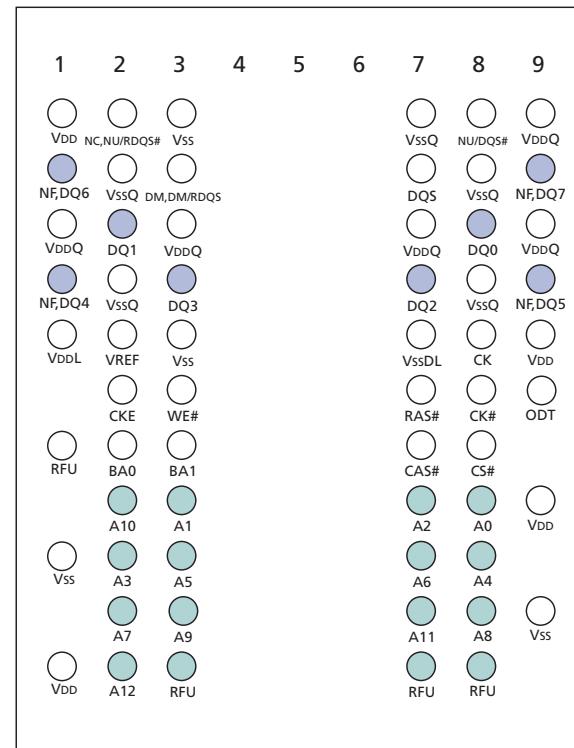

| Figure 2:  | 60-Ball FBGA Pin Assignment (x 4, x 8), 8mm x 12mm (Top View) .....       | 6  |

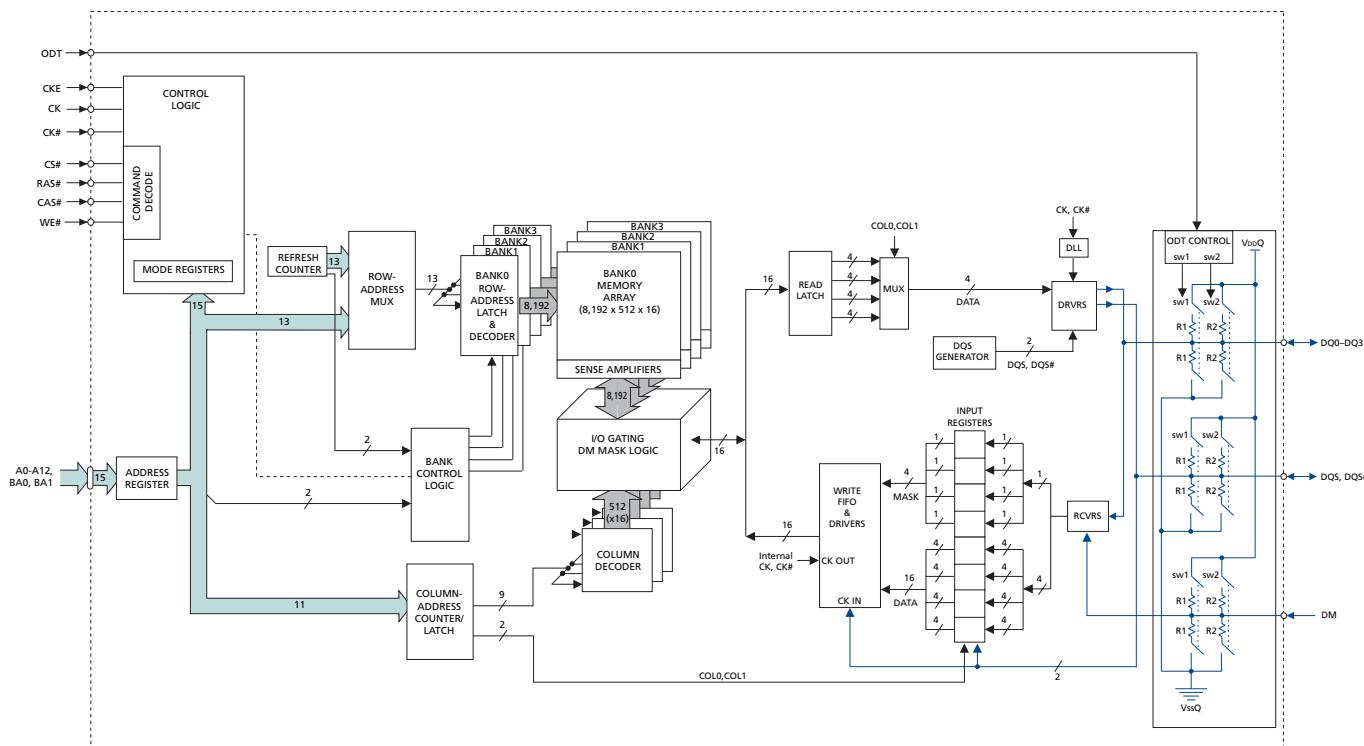

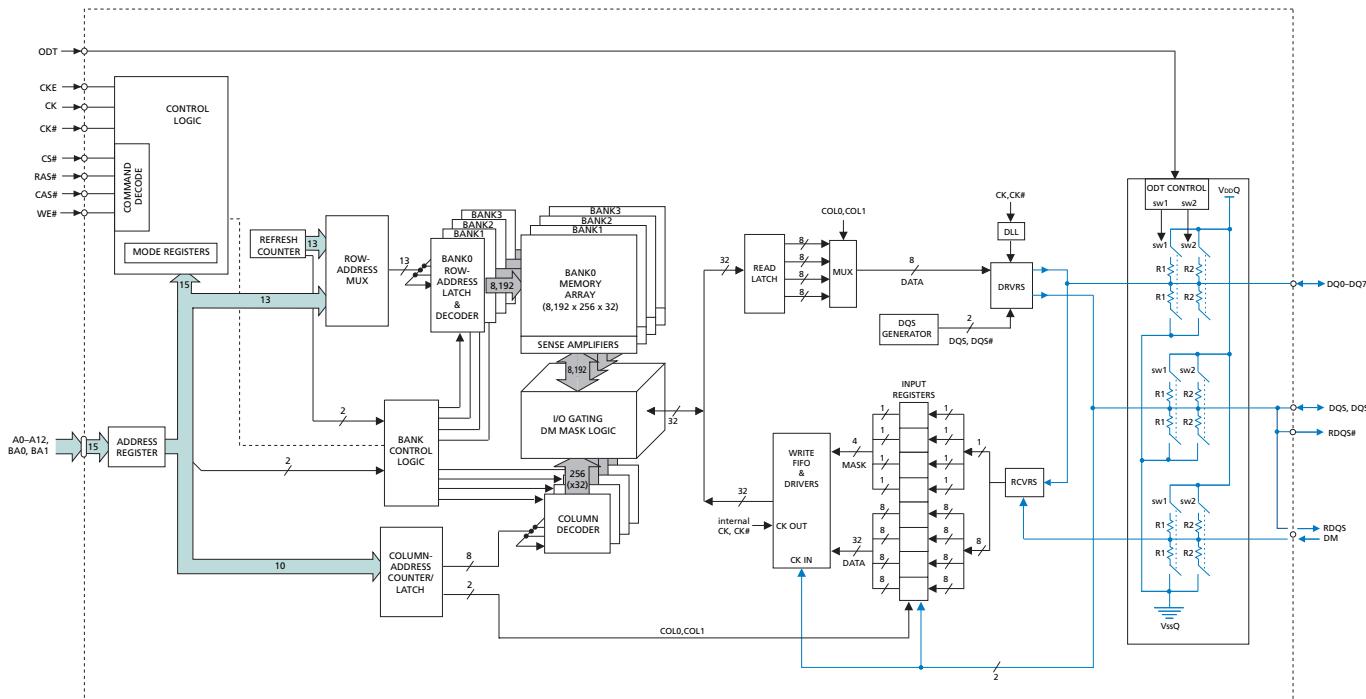

| Figure 3:  | Functional Block Diagram (64 Meg x 4) .....                               | 10 |

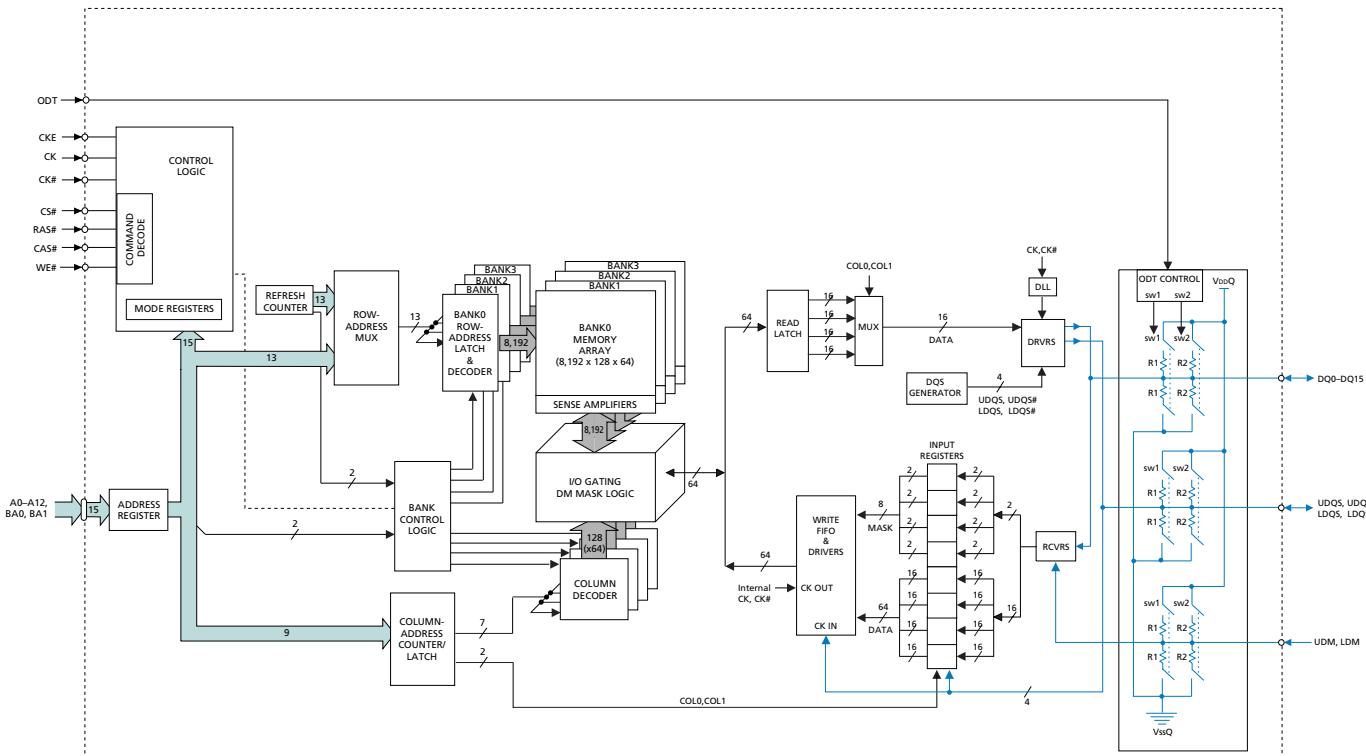

| Figure 4:  | Functional Block Diagram (32 Meg x 8) .....                               | 11 |

| Figure 5:  | Functional Block Diagram (16 Meg x 16) .....                              | 11 |

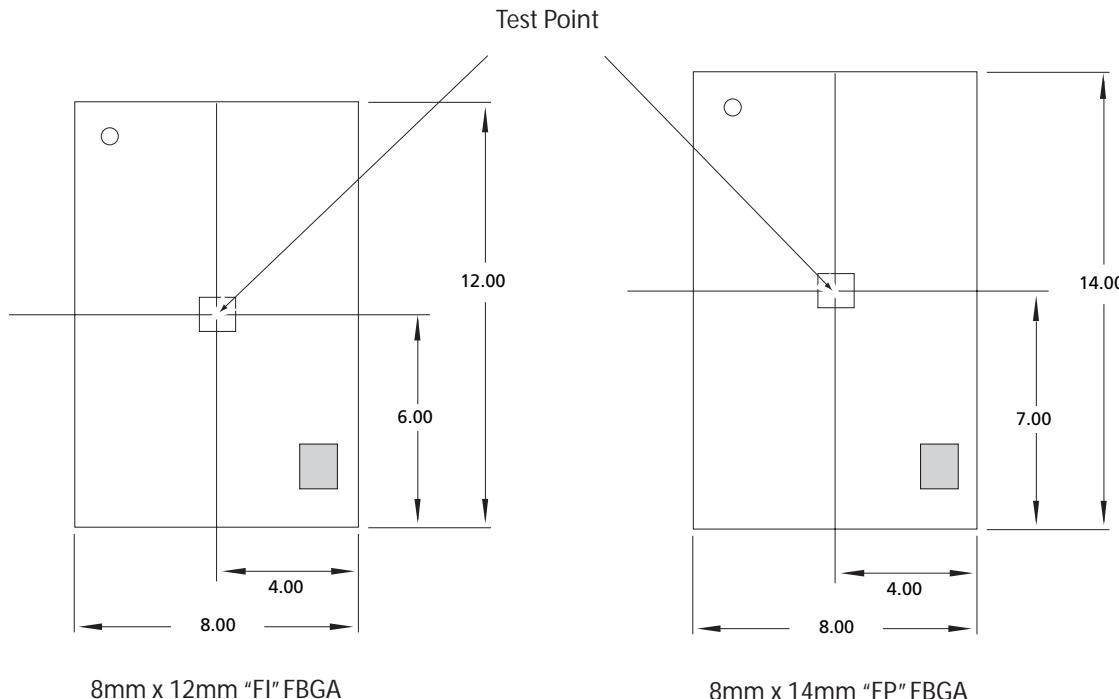

| Figure 6:  | Example Temperature Test Point Location .....                             | 12 |

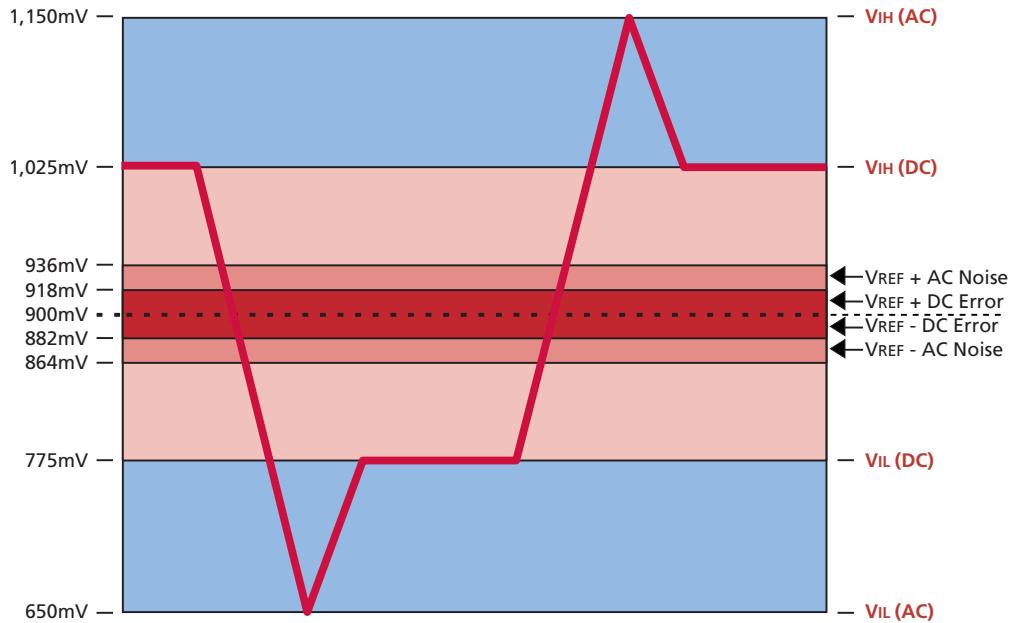

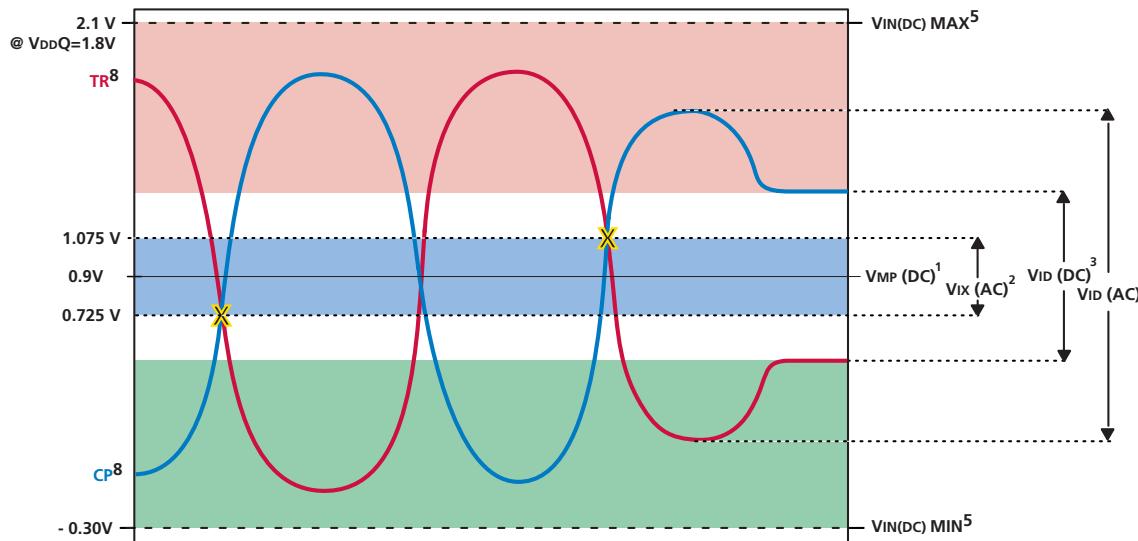

| Figure 7:  | Single-Ended Input Signal Levels .....                                    | 14 |

| Figure 8:  | Differential Input Signal Levels .....                                    | 15 |

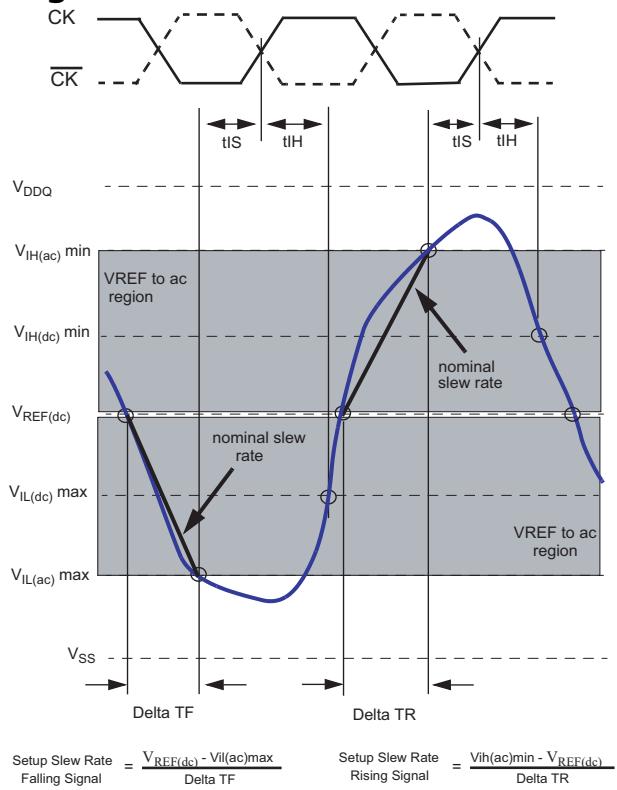

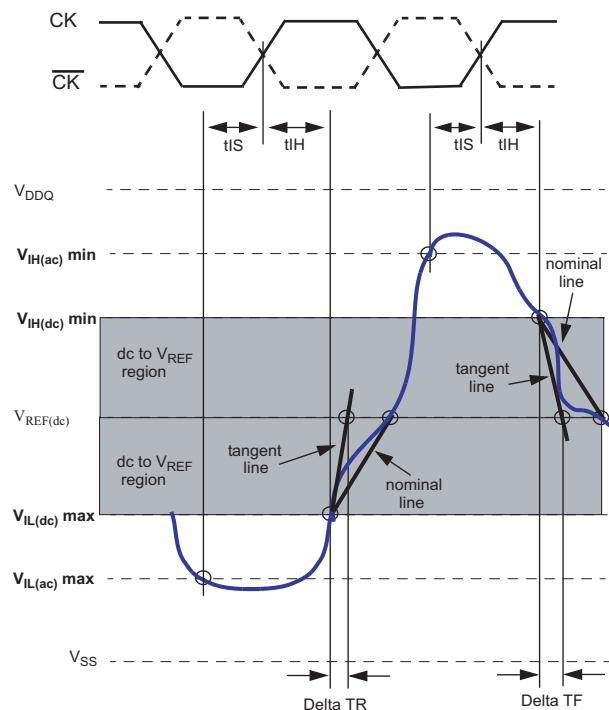

| Figure 9:  | Nominal Slew Rate for $t_{IS}$ .....                                      | 18 |

| Figure 10: | Tangent Line for $t_{IS}$ .....                                           | 18 |

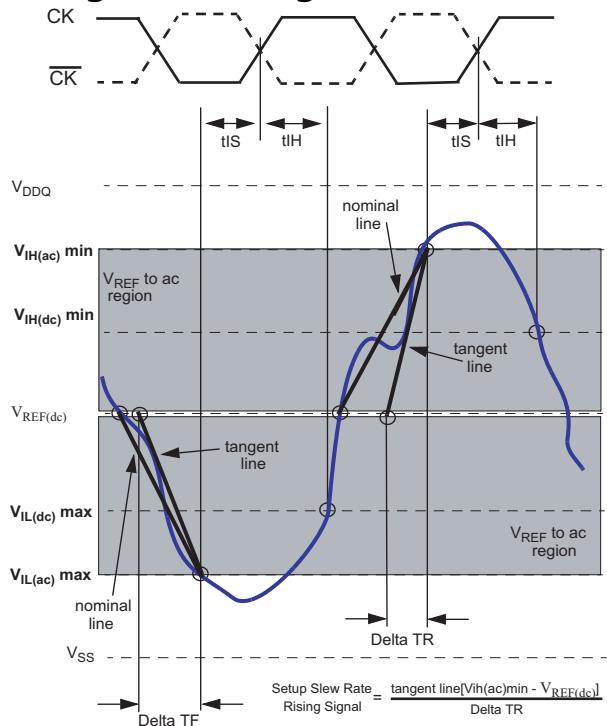

| Figure 11: | Nominal Slew Rate for $t_{IH}$ .....                                      | 19 |

| Figure 12: | Tangent Line for $t_{IH}$ .....                                           | 19 |

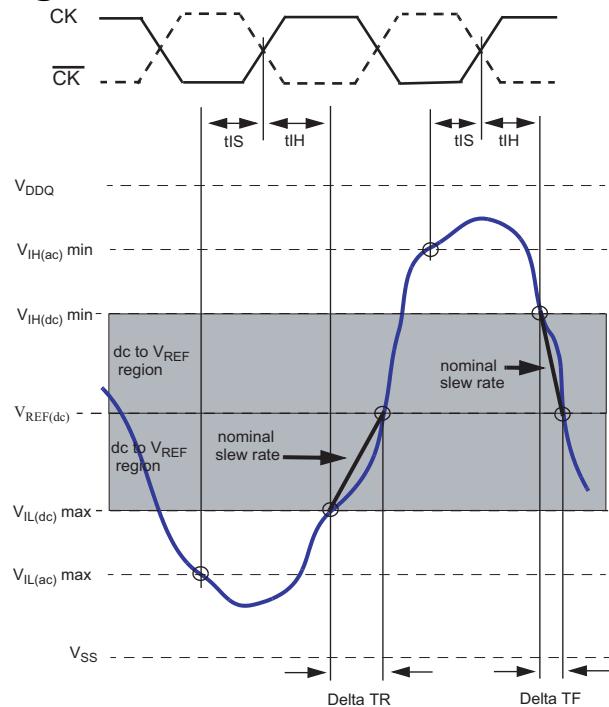

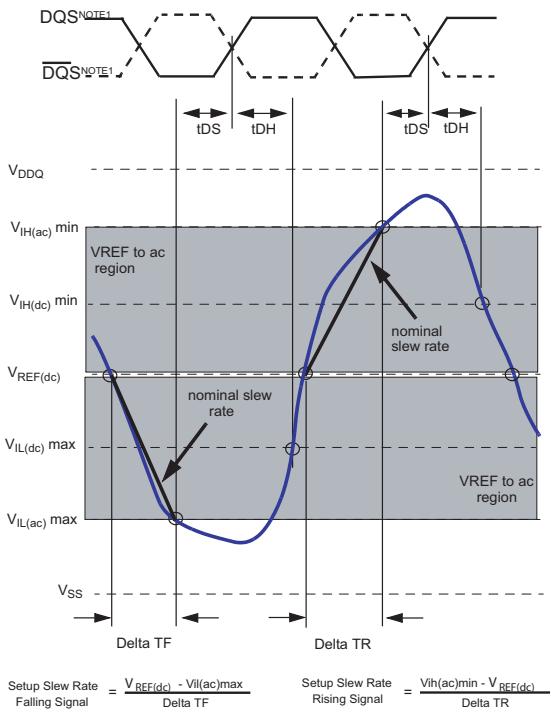

| Figure 13: | Nominal Slew Rate for $t_{DS}$ .....                                      | 21 |

| Figure 14: | Tangent Line for $t_{DS}$ .....                                           | 21 |

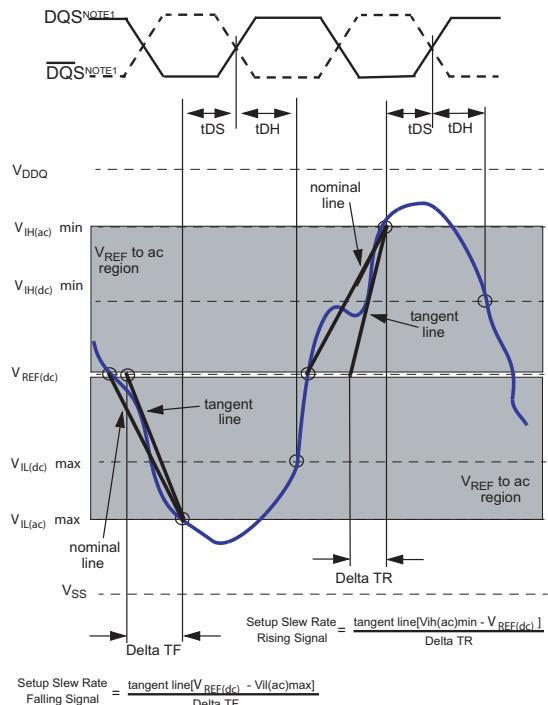

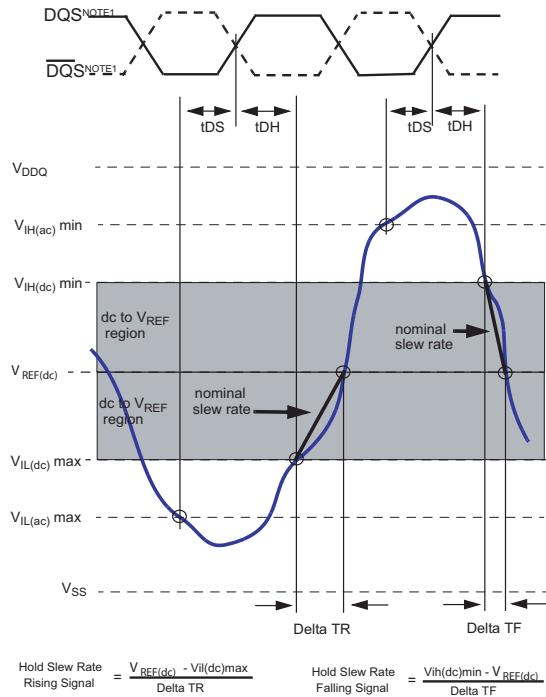

| Figure 15: | Nominal Slew Rate for $t_{DH}$ .....                                      | 22 |

| Figure 16: | Tangent Line for $t_{DH}$ .....                                           | 22 |

| Figure 17: | AC Input Test Signal Waveform Command/Address pins .....                  | 23 |

| Figure 18: | AC Input Test Signal Waveform for Data with DQS,DQS# (differential) ..... | 23 |

| Figure 19: | AC Input Test Signal Waveform for Data with DQS (single-ended) .....      | 24 |

| Figure 20: | AC Input Test Signal Waveform (differential) .....                        | 24 |

| Figure 21: | Input Clamp Characteristics .....                                         | 25 |

| Figure 22: | Overshoot .....                                                           | 26 |

| Figure 23: | Undershoot .....                                                          | 26 |

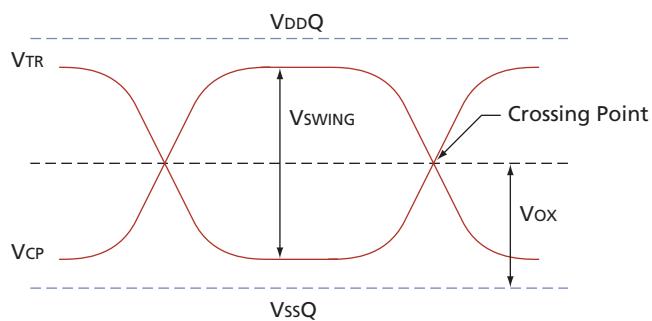

| Figure 24: | Differential Output Signal Levels .....                                   | 27 |

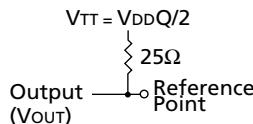

| Figure 25: | Output Slew Rate Load .....                                               | 28 |

| Figure 26: | Full Strength Pull-Down Characteristics .....                             | 29 |

| Figure 27: | Full Strength Pull-up Characteristics .....                               | 30 |

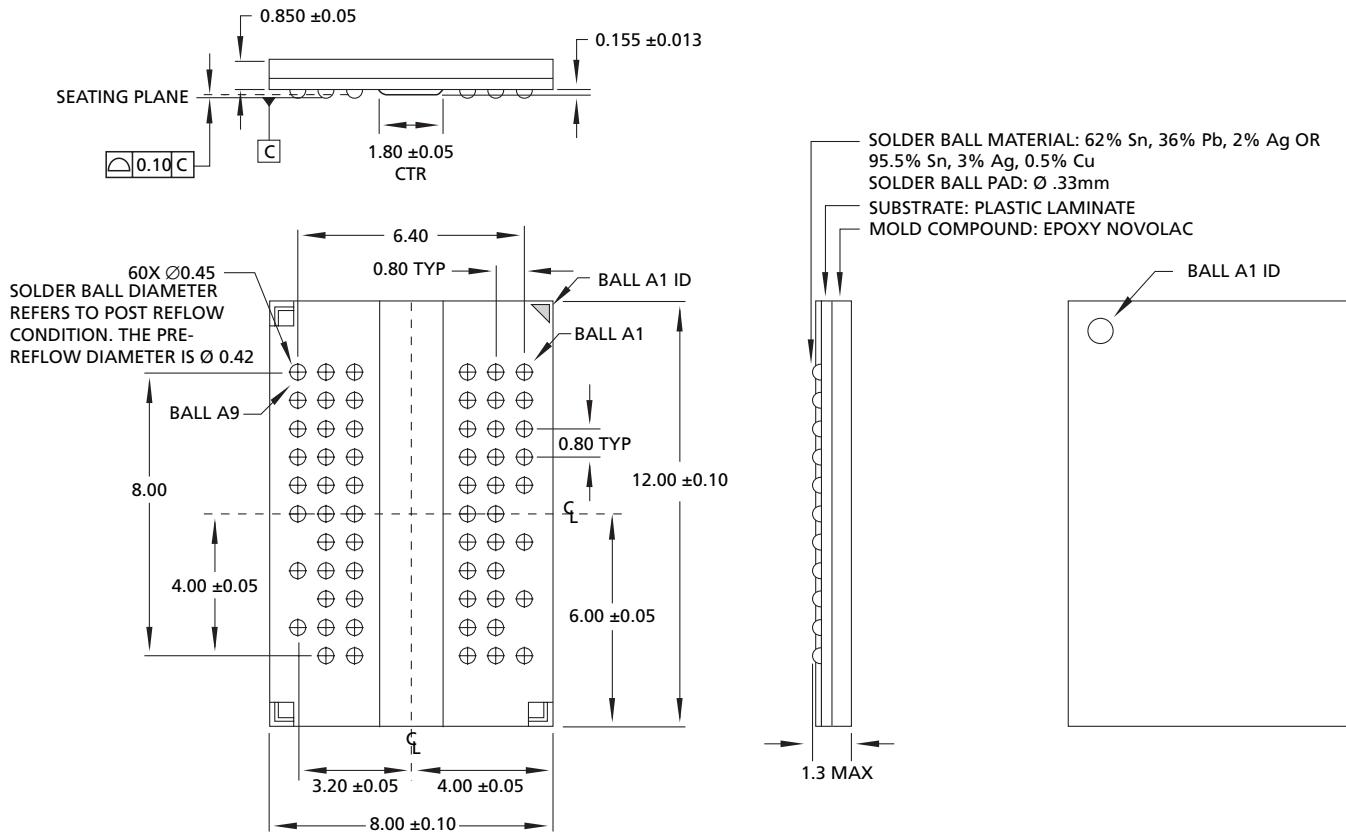

| Figure 28: | Package Drawing 60-Ball (8mm x 12mm) FBGA .....                           | 40 |

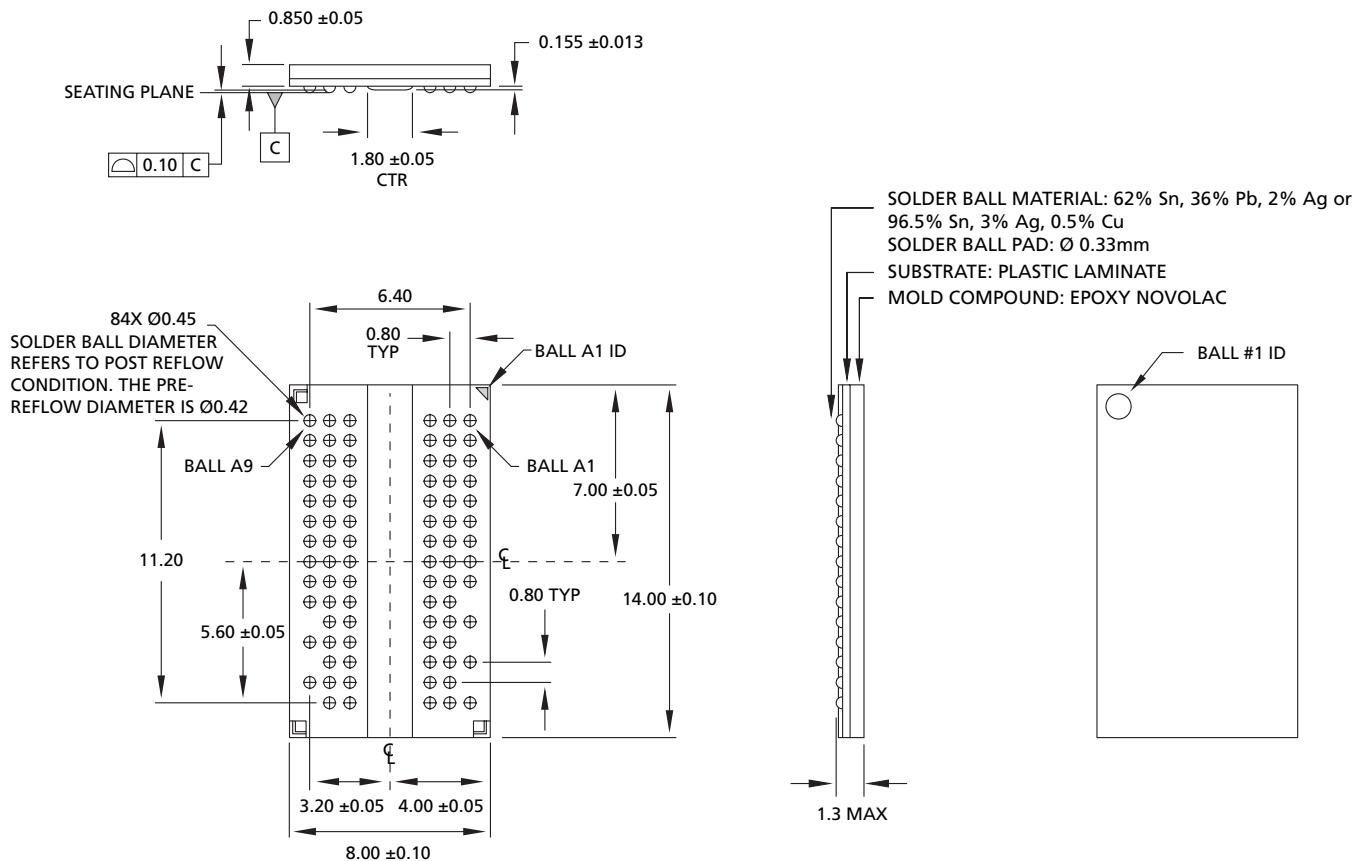

| Figure 29: | Package Drawing 84-Ball (8mm x 14mm) FBGA .....                           | 41 |

## List of Tables

|           |                                                                  |    |

|-----------|------------------------------------------------------------------|----|

| Table 1:  | Key Timing Parameters .....                                      | 1  |

| Table 2:  | FBGA Ball Descriptions 64 Meg x 4, 32 Meg x 8, 16 Meg x 16 ..... | 7  |

| Table 3:  | Absolute Maximum DC Ratings .....                                | 12 |

| Table 4:  | Recommended DC Operating Conditions (SSTL_18).....               | 13 |

| Table 5:  | ODT DC Electrical Characteristics .....                          | 13 |

| Table 6:  | Input DC Logic Levels .....                                      | 14 |

| Table 7:  | Input AC Logic Levels .....                                      | 14 |

| Table 8:  | Differential Input Logic Levels.....                             | 15 |

| Table 9:  | AC Input Test Conditions .....                                   | 16 |

| Table 10: | Setup and Hold Time Derating Values.....                         | 17 |

| Table 11: | <sup>t</sup> DS, <sup>t</sup> DH Derating Values .....           | 20 |

| Table 12: | Input Clamp Characteristics .....                                | 25 |

| Table 13: | Address and Control Pins .....                                   | 26 |

| Table 14: | Clock, Data, Strobe, and Mask Pins .....                         | 26 |

| Table 15: | Differential AC Output Parameters.....                           | 27 |

| Table 16: | Output DC Current Drive .....                                    | 28 |

| Table 17: | Output Characteristics.....                                      | 28 |

| Table 18: | Pulldown Current (mA).....                                       | 29 |

| Table 19: | Pull-Up Current (mA) .....                                       | 30 |

| Table 20: | Input Capacitance .....                                          | 31 |

| Table 21: | DDR2 IDD Specifications and Conditions .....                     | 32 |

| Table 22: | General IDD Parameters .....                                     | 33 |

| Table 23: | IDD7 Timing Patterns .....                                       | 34 |

| Table 24: | AC Operating Conditions .....                                    | 34 |

## FBGA Part Marking Decoder

Due to space limitations, FBGA-packaged components have an abbreviated part marking that is different from the part number. SpecTek's new FBGA part marking decoder makes it easier to understand FBGA part marking. Visit the SpecTek web site at [www.spectek.com/pdfs/fbga\\_decoder.pdf](http://www.spectek.com/pdfs/fbga_decoder.pdf).

## General Description

The 256Mb DDR2 SDRAM is a high-speed, CMOS dynamic random-access memory containing 268,435,456 bits. It is internally configured as a quad-bank DRAM. The functional block diagrams of the 16 Meg x 16, 32 Meg x 8, and 64 Meg x 4 devices, respectively are shown in the Functional Description section. Ball assignments for the 64 Meg x 4 are shown in Figure 1 and signal descriptions are shown in Table 1. Ball assignments for the 32 Meg x 8 and 64 Meg x 4 are shown in Figure 2 and signal descriptions are shown in Table 2.

The 256Mb DDR2 SDRAM uses a double data rate architecture to achieve high-speed operation. The double data rate architecture is essentially a  $4n$ -prefetch architecture with an interface designed to transfer two data words per clock cycle at the I/O pins. A single read or write access for the 256Mb DDR2 SDRAM effectively consists of a single  $4n$ -bit-wide, one-clock-cycle data transfer at the internal DRAM core and four corresponding  $n$ -bit-wide, one-half-clock-cycle data transfers at the I/O pins.

A bidirectional data strobe (DQS, DQS#) is transmitted externally, along with data, for use in data capture at the receiver. DQS is a strobe transmitted by the DDR2 SDRAM during READs and by the memory controller during WRITEs. DQS is edge-aligned with data for READs and center-aligned with data for WRITEs. The x16 offering has two data strobes, one for the lower byte (LDQS, LDQS#) and one for the upper byte (UDQS, UDQS#).

The 256Mb DDR2 SDRAM operates from a differential clock (CK and CK#); the crossing of CK going HIGH and CK# going LOW will be referred to as the positive edge of CK. Commands (address and control signals) are registered at every positive edge of CK. Input data is registered on both edges of DQS, and output data is referenced to both edges of DQS, as well as to both edges of CK.

Read and write accesses to the DDR2 SDRAM are burst-oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with the registration of an ACTIVE command, which is then followed by a READ or WRITE command. The address bits registered coincident with the ACTIVE command are used to select the bank and row to be accessed. The address bits registered coincident with the READ or WRITE command are used to select the bank and the starting column location for the burst access.

The DDR2 SDRAM provides for programmable read or write burst lengths of four or eight locations. DDR2 SDRAM supports interrupting a burst read of eight with another read, or a burst write of eight with another write. An auto precharge function may be enabled to provide a self-timed row precharge that is initiated at the end of the burst access.

As with standard DDR SDRAMs, the pipelined, multibank architecture of DDR2 SDRAMs allows for concurrent operation, thereby providing high, effective bandwidth by hiding row precharge and activation time.

A self refresh mode is provided, along with a power-saving power-down mode.

All inputs are compatible with the JEDEC standard for SSTL\_18. All full drive-strength outputs are SSTL\_18-compatible.

NOTE: 1. The functionality and the timing specifications discussed in this data sheet are for the DLL-enabled mode of operation.

2. Throughout the data sheet, the various figures and text refer to DQs as "DQ." The DQ term is to be interpreted as any and all DQ collectively, unless specifically stated otherwise. Additionally, the x16 is divided into two bytes, the lower byte and upper byte. For the lower byte (DQ0 through DQ7) DM refers to LDM and DQS refers to LDQS. For the upper byte (DQ8 through DQ15) DM refers to UDM and DQS refers to UDQS.

3. Complete functionality is described throughout the document and any page or diagram may have been simplified to convey a topic and may not be inclusive of all requirements.

4. Any specific requirement takes precedence over a general statement.

**Figure 1: 84-ball FBGA Pin Assignment

(x16), 8mm x 14mm (Top View)**

**Figure 2: 60-Ball FBGA Pin Assignment

(x 4, x 8), 8mm x 12mm (Top View)**

**Table 2: FBGA Ball Descriptions 64 Meg x 4, 32 Meg x 8, 16 Meg x 16**

| <b>x16 FBGA BALL ASSIGNMENT</b> | <b>x4, x8 FBGA BALL ASSIGNMENT</b> | <b>SYMBOL</b>   | <b>TYPE</b> | <b>DESCRIPTION</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------|------------------------------------|-----------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| K9                              | F9                                 | ODT             | Input       | On-Die Termination: ODT (registered HIGH) enables termination resistance internal to the DDR2 SDRAM. When enabled, ODT is only applied to each of the following pins: DQ0–DQ15, LDM, UDM, LDQS, LDQS#, UDQS, and UDQS# for the x16; DQ0–DQ7, DQS, DQS#, RDQS, RDQS#, and DM for the x8; DQ0–DQ3, DQS, DQS#, and DM for the x4. The ODT input will be ignored if disabled via the LOAD MODE command.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| J8, K8                          | E8, F8                             | CK, CK#         | Input       | Clock: CK and CK# are differential clock inputs. All address and control input signals are sampled on the crossing of the positive edge of CK and negative edge of CK#. Output data (DQs and DQS/DQS#) is referenced to the crossings of CK and CK#.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| K2                              | F2                                 | CKE             | Input       | Clock Enable: CKE (registered HIGH) activates and CKE (registered LOW) deactivates clocking circuitry on the DDR2 SDRAM. The specific circuitry that is enabled/disabled is dependent on the DDR2 SDRAM configuration and operating mode. CKE LOW provides PRECHARGE POWER-DOWN and SELF REFRESH operations (all banks idle), or ACTIVE POWER-DOWN (row ACTIVE in any bank). CKE is synchronous for POWER-DOWN entry, POWER-DOWN exit, output disable, and for SELF REFRESH entry. CKE is asynchronous for SELF REFRESH exit. Input buffers (excluding CK, CK#, CKE, and ODT) are disabled during POWER-DOWN. Input buffers (excluding CKE) are disabled during SELF REFRESH. CKE is an SSTL_18 input but will detect a LVCMOS LOW level once Vdd is applied during first power-up. After Vref has become stable during the power on and initialization sequence, it must be maintained for proper operation of the CKE receiver. For proper self-refresh operation VREF must be maintained. |

| L8                              | G8                                 | CS#             | Input       | Chip Select: CS# enables (registered LOW) and disables (registered HIGH) the command decoder. All commands are masked when CS# is registered HIGH. CS# provides for external bank selection on systems with multiple ranks. CS# is considered part of the command code.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| K7, L7, K3                      | F7, G7, F3                         | RAS#, CAS#, WE# | Input       | Command Inputs: RAS#, CAS#, and WE# (along with CS#) define the command being entered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| F3, B3                          | B3                                 | LDM, UDM        | Input       | Input Data Mask: DM is an input mask signal for write data. Input data is masked when DM is sampled HIGH along with that input data during a WRITE access. DM is sampled on both edges of DQS. Although DM pins are input-only, the DM loading is designed to match that of DQ and DQS pins. LDM is DM for lower byte DQ0–DQ7 and UDM is DM for upper byte DQ8–DQ15.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| L2, L3                          | G2, G3                             | BA0, BA1        | Input       | Bank Address Inputs: BA0 and BA1 define to which bank an ACTIVE, READ, WRITE, or PRECHARGE command is being applied. BA0 and BA1 define which mode register including MR, EMR, EMR(2), and EMR(3) is loaded during the LOAD MODE command.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

**Table 2: FBGA Ball Descriptions 64 Meg x 4, 32 Meg x 8, 16 Meg x 16**

| <b>x16 FBGA<br/>BALL<br/>ASSIGNMENT</b>                        | <b>x4, x8 FBGA<br/>BALL<br/>ASSIGNMENT</b>         | <b>SYMBOL</b> | <b>TYPE</b> | <b>DESCRIPTION</b>                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------|----------------------------------------------------|---------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M8, M3, M7, N2, N8, N3, N7, P2, P8, P3, M2, P7, R2             | H8, H3, H7, J2, J8, J3, J7, K2, K8, K3, H2, K7, L2 | A0-A12        | Input       | Address Inputs: Provide the row address for ACTIVE commands, and the column address and auto precharge bit (A10) for Read/Write commands, to select one location out of the memory array in the respective bank. A10 sampled during a PRECHARGE command determines whether the PRECHARGE applies to one bank (A10 LOW, bank selected by BA0, BA1) or all banks (A10 HIGH). The address inputs also provide the op-code during a LOAD MODE command. |

| G8, G2, H7, H3, H1, H9, F1, F9, C8, C2, D7, D3, D1, D9, B1, B9 | –                                                  | DQ0–DQ15      | I/O         | Data Input/Output: Bidirectional data bus for 16 Meg x 16.                                                                                                                                                                                                                                                                                                                                                                                         |

| –                                                              | C8, C2, D7, D3, D1, D9, B1, B9                     | DQ0–DQ7       | I/O         | Data Input/Output: Bidirectional data bus for 32 Meg x 8.                                                                                                                                                                                                                                                                                                                                                                                          |

| –                                                              | C8, C2, D7, D3                                     | DQ0–DQ3       | I/O         | Data Input/Output: Bidirectional data bus for 64 Meg x 4.                                                                                                                                                                                                                                                                                                                                                                                          |

| B7, A8                                                         | –                                                  | UDQS, UDQS#   | I/O         | Data Strobe for Upper Byte: Output with read data, input with write data for source synchronous operation. Edge-aligned with read data, center-aligned with write data. UDQS# is only used when differential data strobe mode is enabled via the LOAD MODE command.                                                                                                                                                                                |

| F7, E8                                                         | –                                                  | LDQS, LDQS#   | I/O         | Data Strobe for Lower Byte: Output with read data, input with write data for source synchronous operation. Edge-aligned with read data, center-aligned with write data. LDQS# is only used when differential data strobe mode is enabled via the LOAD MODE command.                                                                                                                                                                                |

| –                                                              | B7, A8                                             | DQS, DQS#     | I/O         | Data Strobe: Output with read data, input with write data for source synchronous operation. Edge-aligned with read data, center aligned with write data. DQS# is only used when differential data strobe mode is enabled via the LOAD MODE command.                                                                                                                                                                                                |

| –                                                              | B3, A2                                             | RDQS, RDQS#   | Output      | Redundant Data Strobe for 32 Meg x 8 only. RDQS is enabled/disabled via the LOAD MODE command to the Extended Mode Register (EMR). When RDQS is enabled, RDQS is output with read data only and is ignored during write data. When RDQS is disabled, pin B3 becomes Data Mask (see DM pin). RDQS# is only used when RDQS is enabled AND differential data strobe mode is enabled.                                                                  |

| A1, E1, J9, M9, R1                                             | A1, E9, H9, L1                                     | VDD           | Supply      | Power Supply: 1.8V $\pm$ 0.1V                                                                                                                                                                                                                                                                                                                                                                                                                      |

| J1                                                             | E1                                                 | VDDL          | Supply      | DLL Power Supply: 1.8V $\pm$ 0.1V                                                                                                                                                                                                                                                                                                                                                                                                                  |

| A9, C1, C3, C7, C9, E9, G1, G3, G7, G9                         | A9, C1, C3, C7, C9                                 | VDDQ          | Supply      | DQ Power Supply: 1.8V $\pm$ 0.1V. Isolated on the device for improved noise immunity.                                                                                                                                                                                                                                                                                                                                                              |

| J2                                                             | E2                                                 | VREF          | Supply      | SSTL_18 reference voltage.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A3, E3, J3, N1, P9                                             | A3, E3, J1, K9                                     | Vss           | Supply      | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| J7                                                             | E7                                                 | VssDL         | Supply      | DLL Ground. Isolated on the device from Vss and VssQ.                                                                                                                                                                                                                                                                                                                                                                                              |

| A7, B2, B8, D2, D8, E7, F2, F8, H2, H8,                        | A7, B2, B8, D2, D8                                 | VssQ          | Supply      | DQ Ground. Isolated on the device for improved noise immunity.                                                                                                                                                                                                                                                                                                                                                                                     |

**Table 2: FBGA Ball Descriptions 64 Meg x 4, 32 Meg x 8, 16 Meg x 16**

| <b>x16 FBGA<br/>BALL<br/>ASSIGNMENT</b> | <b>x4, x8 FBGA<br/>BALL<br/>ASSIGNMENT</b> | <b>SYMBOL</b> | <b>TYPE</b> | <b>DESCRIPTION</b>                                                                                                                                     |

|-----------------------------------------|--------------------------------------------|---------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| A2, E2                                  | A2, B1, B9, D1, D9                         | NC            | –           | No Connect: These pins should be left unconnected.                                                                                                     |

|                                         | D1, D9, B1, B9                             | NF            | -           | No Function: These pins are used as DQ4-DQ7 on the 32 Meg x 8, but are NF (No Function) on the 16 Meg x 16 configuration.                              |

| A8, E8                                  | A2, A8                                     | NU            | –           | Not Used: If EMR[E10] = 0, A8 and E8 are UDQS# and LDQS#. If EMR[E10] = 1, then A8 and E8 are Not Used.                                                |

| L1, R3, R7, R8                          | G1, L3, L7, L8                             | RFU           | –           | Reserved for Future Use; Bank address bit BA2(L1) for 1Gb, 2Gb, and 4Gb densities. Row address bits A13(R8), A14(R3) and A15(R7) for higher densities. |

## Functional Description

The 256Mb DDR2 SDRAM is a high-speed, CMOS dynamic random-access memory containing 268,435,456 bits. The 256Mb DDR2 SDRAM is internally configured as a four-bank DRAM.

The 256Mb DDR2 SDRAM uses a double data rate architecture to achieve high-speed operation. The DDR2 architecture is essentially a  $4n$ -prefetch architecture, with an interface designed to transfer two data words per clock cycle at the I/O pins. A single read or

write access for the 256Mb DDR2 SDRAM consists of a single  $4n$ -bit-wide, one-clock-cycle data transfer at the internal DRAM core and four corresponding  $n$ -bit-wide, one-half-clock-cycle data transfers at the I/O pins.

Prior to normal operation, the DDR2 SDRAM must be initialized. The following sections provide detailed information covering device initialization, register definition, command descriptions, and device operation.

**Figure 3: Functional Block Diagram (64 Meg x 4)**

**Figure 4: Functional Block Diagram (32 Meg x 8)**

**Figure 5: Functional Block Diagram (16 Meg x 16)**

## Absolute Maximum Ratings

Stresses greater than those listed may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the opera-

tional sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

**Table 3: Absolute Maximum DC Ratings**

| Symbol            | Parameter                                                                                               | Min  | Max | Units |

|-------------------|---------------------------------------------------------------------------------------------------------|------|-----|-------|

| VDD               | VDD Supply Voltage Relative to Vss                                                                      | -1.0 | 2.3 | V     |

| VDDQ              | VDDQ Supply Voltage Relative to VssQ                                                                    | -0.5 | 2.3 | V     |

| VDDL              | VDDL Supply Voltage Relative to VssL                                                                    | -0.5 | 2.3 | V     |

| VIN, VOUT         | Voltage on any Pin Relative to Vss                                                                      | -0.5 | 2.3 | V     |

| TSTG              | Storage Temperature ( $T_{case}$ ) <sup>1</sup>                                                         | -55  | 100 | °C    |

| T <sub>C</sub>    | Operating Temperature ( $T_{case}$ ) <sup>1, 2</sup>                                                    | 0    | 70  | °C    |

| I <sub>I</sub>    | Input Leakage Current<br>Any input $0V \leq V_{IN} \leq V_{DD}$<br>(All other pins not under test = 0V) | -5   | 5   | µA    |

| I <sub>OZ</sub>   | Output Leakage Current<br>$0V \leq V_{OUT} \leq V_{DDQ}$<br>DQs and ODT are disabled                    | -5   | 5   | µA    |

| I <sub>VREF</sub> | VREF Leakage Current<br>VREF = Valid VREF level                                                         | -2   | 2   | µA    |

NOTE:

1. MAX operating case temperature;  $T_C$  is measured in the center of the package illustrated in Figure 6.

2. Device functionality is not guaranteed if the DRAM device exceeds the maximum  $T_C$  during operation.

**Figure 6: Example Temperature Test Point Location**

8mm x 12mm "FI" FBGA

8mm x 14mm "FP" FBGA

## AC and DC Operating Conditions

**Table 4: Recommended DC Operating Conditions (SSTL\_18)**

All voltages referenced to Vss

| Parameter                        | Symbol   | Min           | Nom         | Max           | Units | Notes |

|----------------------------------|----------|---------------|-------------|---------------|-------|-------|

| Supply Voltage                   | VDD      | 1.7           | 1.8         | 1.9           | V     | 1, 5  |

| VDDL Supply Voltage              | VDDL     | 1.7           | 1.8         | 1.9           | V     | 4, 5  |

| I/O Supply Voltage               | VDDQ     | 1.7           | 1.8         | 1.9           | V     | 4, 5  |

| I/O Reference Voltage            | VREF(DC) | 0.49 x VDDQ   | 0.50 x VDDQ | 0.51 x VDDQ   | V     | 2     |

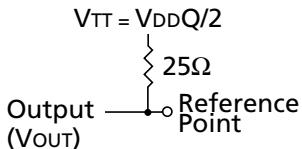

| I/O Termination Voltage (system) | VTT      | VREF(DC) - 40 | VREF(DC)    | VREF(DC) + 40 | mV    | 3     |

NOTE:

1. VDD and VDDQ must track each other. VDDQ must be less than or equal to VDD.

2. VREF is expected to equal VDDQ/2 of the transmitting device and to track variations in the DC level of the same. Peak-to-peak noise (non-common mode) on VREF may not exceed  $\pm 1\%$  of the DC value. Peak-to-peak AC noise on VREF may not exceed  $\pm 2$  percent of VREF(dc). This measurement is to be taken at the nearest VREF bypass capacitor.

3. VTT is not applied directly to the device. VTT is a system supply for signal termination resistors, is expected to be set equal to VREF and must track variations in the DC level of VREF.

4. VDDQ tracks with VDD; VDDL tracks with VDD.

5. VssQ = VssL = Vss

**Table 5: ODT DC Electrical Characteristics**

All voltages referenced to Vss

| Parameter                                                             | Symbol    | Min | Nom | Max | Units | Notes |

|-----------------------------------------------------------------------|-----------|-----|-----|-----|-------|-------|

| RTT effective impedance value for 75Ω setting<br>EMR (A6, A2) = 0, 1  | RTT1(EFF) | 60  | 75  | 90  | Ω     | 1     |

| RTT effective impedance value for 150Ω setting<br>EMR (A6, A2) = 1, 0 | RTT2(EFF) | 120 | 150 | 180 | Ω     | 1     |

| Deviation of VM with respect to VDDQ/2                                | ΔVM       | -6% |     | 6%  | %     | 2     |

NOTE:

1. RTT1(EFF) and RTT2(EFF) are determined by applying VIH(AC) and VIL(AC) to pin under test separately, then measure current I(VIH(AC)) and I(VIL(AC)) respectively.

$$RTT(EFF) = \frac{VIH(AC) - VIL(AC)}{I(VIH(AC)) - I(VIL(AC))}$$

2. Measure voltage (VM) at tested pin with no load.

$$\Delta VM = \left( \frac{2 \times VM}{VDDQ} - 1 \right) \times 100\%$$

## Input Electrical Characteristics and Operating Conditions

**Table 6: Input DC Logic Levels**

All voltages referenced to Vss

| Parameter                    | Symbol  | Min            | Max            | Units | Notes |

|------------------------------|---------|----------------|----------------|-------|-------|

| Input High (Logic 1) Voltage | VIH(DC) | VREF(DC) + 125 | VDDQ + 300     | mV    |       |

| Input Low (Logic 0) Voltage  | VIL(DC) | -300           | VREF(DC) - 125 | mV    |       |

**Table 7: Input AC Logic Levels**

All voltages referenced to Vss

| Parameter                    | Symbol  | Min            | Max            | Units | Notes |

|------------------------------|---------|----------------|----------------|-------|-------|

| Input High (Logic 1) Voltage | VIH(AC) | VREF(DC) + 250 | -              | mV    |       |

| Input Low (Logic 0) Voltage  | VIL(AC) | -              | VREF(DC) - 250 | mV    |       |

**Figure 7: Single-Ended Input Signal Levels**

NOTE:

Numbers in diagram reflect nominal values.

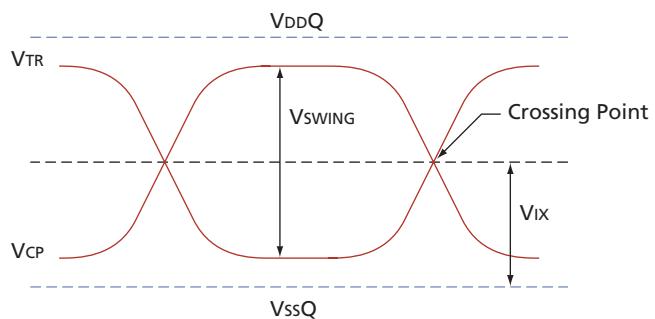

**Table 8: Differential Input Logic Levels**

All voltages referenced to Vss

| Parameter                           | Symbol  | Min               | Max               | Units | Notes |

|-------------------------------------|---------|-------------------|-------------------|-------|-------|

| DC Input Signal Voltage             | VIN(DC) | -300              | VDDQ + 300        | mV    | 1     |

| DC Differential Input Voltage       | VID(DC) | 250               | VDDQ + 600        | mV    | 2     |

| AC Differential Input Voltage       | VID(AC) | 500               | VDDQ + 600        | mV    | 3     |

| AC Differential Cross-Point Voltage | Vix(AC) | 0.50 x VDDQ - 175 | 0.50 x VDDQ + 175 | mV    | 4     |

| Input Midpoint Voltage              | VMP(DC) | 850               | 950               | mV    | 5     |

NOTE:

1. VIN (DC) specifies the allowable DC execution of each input of differential pair such as CK, CK#, DQS, DQS#, LDQS, LDQS#, UDQS, UDQS#, and RDQS, RDQS#.

2. VID (DC) specifies the input differential voltage | VTR - VCP | required for switching, where VTR is the true input (such as CK, DQS, LDQS, UDQS, RDQS) level and VCP is the complementary input (such as CK#, DQS#, LDQS#, UDQS#, RDQS#). The minimum value is equal to VIH(DC) - VIL(DC). Differential input signal levels are shown in Figure 8.

3. VID(AC) specifies the input differential voltage | VTR - VCP | required for switching, where VTR is the true input (such as CK, DQS, LDQS, UDQS, RDQS) level and VCP is the complementary input (such as CK#, DQS#, LDQS#, UDQS#, RDQS#). The minimum value is equal to VIH(AC) - VIL(AC) from Table 7 on page 14.

4. The typical value of Vix (AC) is expected to be about 0.5 x VDDQ of the transmitting device and Vix(AC) is expected to track variations in VDDQ. Vix(AC) indicates the voltage at which differential input signals must cross as shown in Figure 8.

5. VMP(DC) specifies the input differential common mode voltage (VTR + VCP)/2 where VTR is the true input (CK, DQS) level and VCP is the complementary input (CK#, DQS#). VMP(DC) is expected to be about 0.5\*VDDQ.

**Figure 8: Differential Input Signal Levels**

NOTE:

1. This provides a minimum of 850mV to a maximum of 950mV and is expected to be VDDQ/2.

2. TR and CP must cross in this region.

3. TR and CP must meet at least VID(DC) min when static and is centered around VMP(DC).

4. TR and CP must have a minimum 500mV peak-to-peak swing.

5. TR and CP may not be more positive than VDDQ + 0.3V or more negative than Vss - 0.3V.

6. For AC operation, all DC clock requirements must also be satisfied.

7. Numbers in diagram reflect nominal values.

8. TR represents the CK, DQS, RDQS, LDQS and UDQS signals; CP represents CK#, DQS#, RDQS#, LDQS# and UDQS# signals.

**Table 9: AC Input Test Conditions**

| Parameter                                                                                                                                                       | Symbol               | Min                    | Max                    | Units | Notes   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------------|------------------------|-------|---------|

| Input setup timing measurement reference level<br>BA1-BA0, A0-A12, CS#, RAS#, CAS#, WE#, ODT, DM, UDM, LDM and CKE                                              | V <sub>RS</sub>      | See Note 2             |                        |       | 1, 2,   |

| Input hold timing measurement reference level<br>BA1-BA0, A0-A12, CS#, RAS#, CAS#, WE#, ODT, DM, UDM, LDM and CKE                                               | V <sub>RH</sub>      | See Note3              |                        |       | 1, 3,   |

| Input timing measurement reference level (single-ended)<br>DQS for x4x8; UDQS, LDQS for x16                                                                     | V <sub>REF(DC)</sub> | V <sub>DDQ</sub> *0.49 | V <sub>DDQ</sub> *0.51 | V     | 1, 4    |

| Input timing measurement reference level (differential)<br>CK, CK# for x4,x8,x16<br>DQS, DQS# for x4,x8; RDQS, RDQS# for x8<br>UDQS, UDQS#, LDQS, LDQS# for x16 | V <sub>RD</sub>      | V <sub>I(X)</sub> (AC) |                        | V     | 1, 5, 6 |

**NOTE:**

1. All voltages referenced to V<sub>SS</sub>.

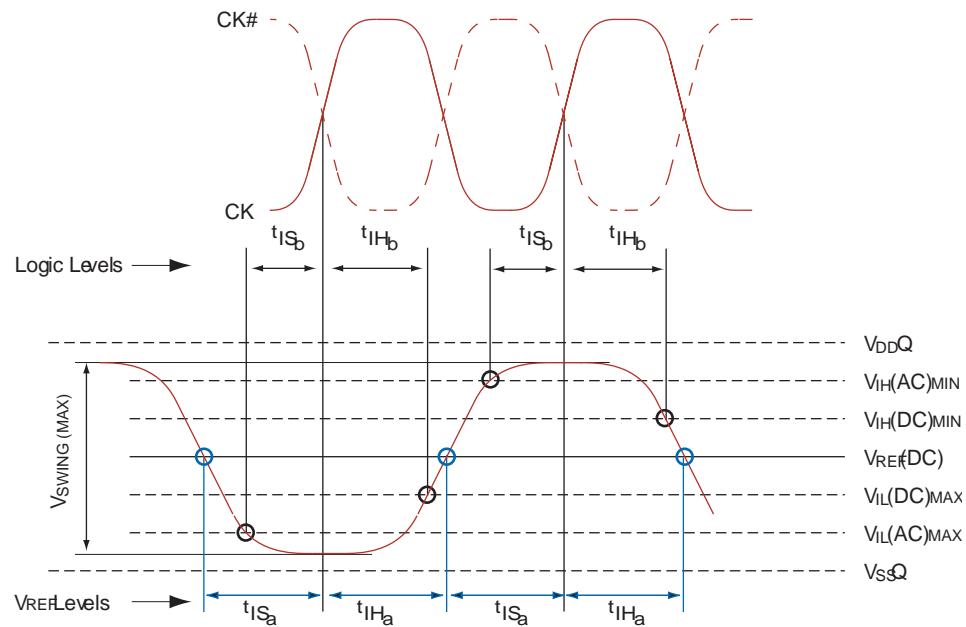

2. Input waveform setup timing ( $t_{IS}$ ) is referenced from the input signal crossing at the V<sub>IH(AC)</sub> level for a rising signal and V<sub>IL(DC)</sub> for a falling signal applied to the device under test as shown in Figure 17.

3. Input waveform hold ( $t_{IH}$ ) timing is referenced from the input signal crossing at the V<sub>IL(DC)</sub> level for a rising signal and V<sub>IH(DC)</sub> for a falling signal applied to the device under test as shown in Figure 17

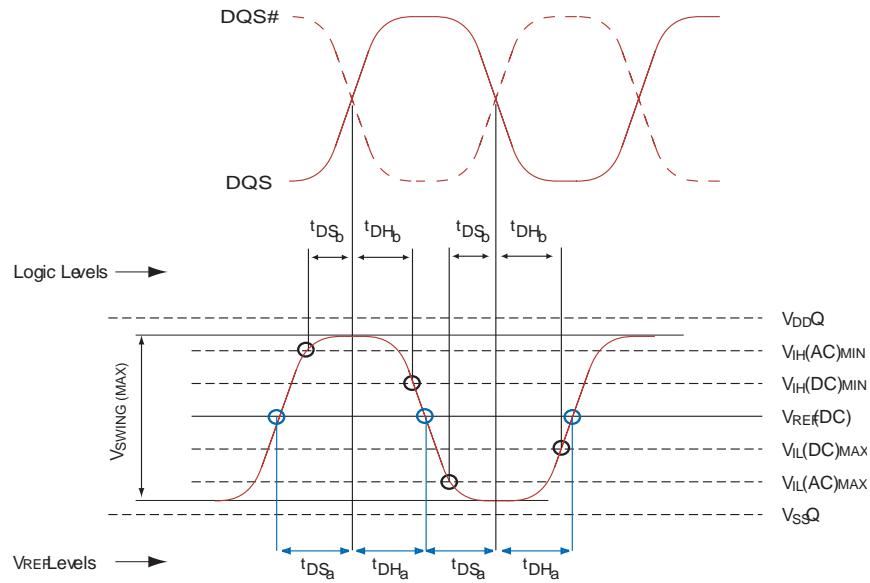

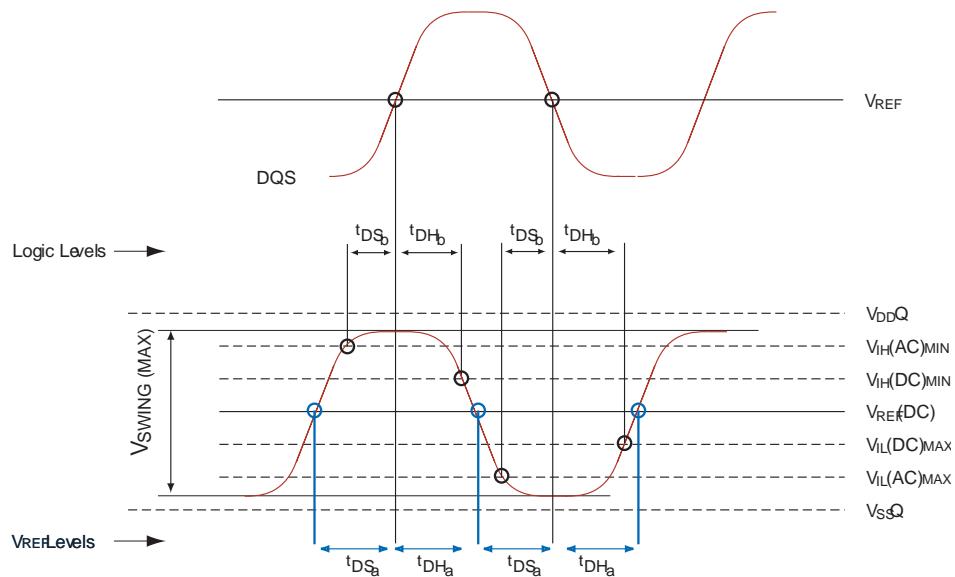

4. Input waveform setup timing ( $t_{DS}$ ) and hold timing ( $t_{DH}$ ) for single-ended data strobe is referenced from the crossing of DQS, UDQS, or LDQS through the V<sub>REF</sub> level applied to the device under test as shown in Figure 19.

5. Input waveform setup timing ( $t_{DS}$ ) and hold timing ( $t_{DH}$ ) when differential data strobe is enabled is referenced from the crosspoint of DQS,DQS# or UDQS,UDQS# or LDQS,LDQS# as shown in Figure 18.

6. Input waveform timing is referenced to the crossing point level (V<sub>I(X)</sub>) of two input signals (V<sub>TR</sub> and V<sub>CP</sub>) applied to the device under test, where V<sub>TR</sub> is the "true" input signal and V<sub>CP</sub> is the "complementary" input signal shown in Figure 20.

7. See "Input Slew Rate Derating" on page 17.

## Input Slew Rate Derating

For all input signals the total  $t_{IS}$  (setup time) and  $t_{IH}$  (hold time) required is calculated by adding the data sheet  $t_{IS(base)}$  and  $t_{IH(base)}$  value to the  $\Delta t_{IS}$  and  $\Delta t_{IH}$  derating value respectively. Example:  $t_{IS}$  (total setup time) =  $t_{IS(base)}$  +  $\Delta t_{IS}$

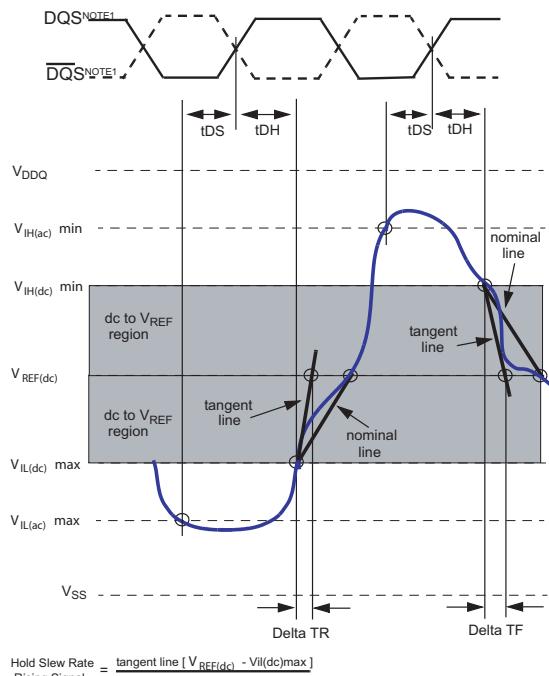

Setup ( $t_{IS}$ ) nominal slew rate for a rising signal is defined as the slew rate between the last crossing of VREF(DC) and the first crossing of VIH(AC)min. Setup ( $t_{IS}$ ) nominal slew rate for a falling signal is defined as the slew rate between the last crossing of VREF(DC) and the first crossing of VIL(AC)MAX. If the actual signal is always earlier than the nominal slew rate line between shaded 'VREF(DC) to AC region', use nominal slew rate for derating value (Figure 9 on page 18) If the actual signal is later than the nominal slew rate line anywhere between shaded 'VREF(DC) to ac region', the slew rate of a tangent line to the actual signal from the AC level to DC level is used for derating value (Figure 10 on page 18)

Hold ( $t_{IH}$ ) nominal slew rate for a rising signal is defined as the slew rate between the last crossing of VIL(DC)MAX and the first crossing of VREF(DC). Hold

( $t_{IH}$ ) nominal slew rate for a falling signal is defined as the slew rate between the last crossing of VIH(DC)MIN and the first crossing of VREF(DC). If the actual signal is always later than the nominal slew rate line between shaded 'dc to VREF(DC) region', use nominal slew rate for derating value (Figure 11 on page 19) If the actual signal is earlier than the nominal slew rate line anywhere between shaded 'dc to VREF(DC) region', the slew rate of a tangent line to the actual signal from the dc level to VREF(DC) level is used for derating value (Figure 12 on page 19)

Although for slow slew rates the total setup time might be negative (i.e. a valid input signal will not have reached VIH/IL(AC) at the time of the rising clock transition) a valid input signal is still required to complete the transition and reach VIH/IL(AC).

For slew rates in between the values listed in Table 10, the derating values may obtained by linear interpolation.

**Table 10: Setup and Hold Time Derating Values**

| Command/<br>Address Slew<br>rate<br>(V/ns) |       | CK,CK# Differential Slew Rate |                 |                 |                 |                 |                 | Units |  |

|--------------------------------------------|-------|-------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-------|--|

|                                            |       | 2.0 V/ns                      |                 | 1.5 V/ns        |                 | 1.0 V/ns        |                 |       |  |

|                                            |       | $\Delta t_{IS}$               | $\Delta t_{IH}$ | $\Delta t_{IS}$ | $\Delta t_{IH}$ | $\Delta t_{IS}$ | $\Delta t_{IH}$ |       |  |

| 4.0                                        | +187  | +94                           | +217            | +124            | +247            | +154            | +154            | ps    |  |

| 3.5                                        | +179  | +89                           | +209            | +119            | +239            | +149            | +149            | ps    |  |

| 3.0                                        | +167  | +83                           | +197            | +113            | +227            | +143            | +143            | ps    |  |

| 2.5                                        | +150  | +75                           | +180            | +105            | +210            | +135            | +135            | ps    |  |

| 2.0                                        | +125  | +45                           | +155            | +75             | +185            | +105            | +105            | ps    |  |

| 1.5                                        | +83   | +21                           | +113            | +51             | +143            | +81             | +81             | ps    |  |

| 1.0                                        | 0     | 0                             | +30             | +30             | +60             | +60             | +60             | ps    |  |

| 0.9                                        | -11   | -14                           | +19             | +16             | +49             | +46             | +46             | ps    |  |

| 0.8                                        | -25   | -31                           | +5              | -1              | +35             | +29             | +29             | ps    |  |

| 0.7                                        | -43   | -54                           | -13             | -24             | +17             | +6              | +6              | ps    |  |

| 0.6                                        | -67   | -83                           | -37             | -53             | -7              | -23             | -23             | ps    |  |

| 0.5                                        | -110  | -125                          | -80             | -95             | -50             | -65             | -65             | ps    |  |

| 0.4                                        | -175  | -188                          | -145            | -158            | -115            | -128            | -128            | ps    |  |

| 0.3                                        | -285  | -292                          | -255            | -262            | -225            | -232            | -232            | ps    |  |

| 0.25                                       | -350  | -375                          | -320            | -345            | -290            | -315            | -315            | ps    |  |

| 0.2                                        | -525  | -500                          | -495            | -470            | -465            | -440            | -440            | ps    |  |

| 0.15                                       | -800  | -708                          | -770            | -678            | -740            | -648            | -648            | ps    |  |

| 0.1                                        | -1450 | -1125                         | -1420           | -1095           | -1390           | -1065           | -1065           | ps    |  |

**Figure 9: Nominal Slew Rate for  $t_{IS}$**

**Figure 10: Tangent Line for  $t_{IS}$**

**Figure 11: Nominal Slew Rate for  $t_{IH}$**

**Figure 12: Tangent Line for  $t_{IH}$**

$$\text{Hold Slew Rate}_{\text{Rising Signal}} = \frac{\text{tangent line} [ V_{REF(dc)} - V_{IL(dc)max} ]}{\Delta TR}$$

$$\text{Hold Slew Rate}_{\text{Falling Signal}} = \frac{\text{tangent line} [ V_{IH(dc)min} - V_{REF(dc)} ]}{\Delta TF}$$

## Data Slew Rating

**Table 11:  $t_{DS}$ ,  $t_{DH}$  Derating Values**

Note 1; all units in ps

|                      |     | DQS,DQS# Differential Slew Rate |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |

|----------------------|-----|---------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

|                      |     | 4.0 V/ns                        |                 | 3.0 V/ns        |                 | 2.0 V/ns        |                 | 1.8 V/ns        |                 | 1.6 V/ns        |                 | 1.4V/ns         |                 | 1.2V/ns         |                 | 1.0V/ns         |                 | 0.8V/ns         |                 |

|                      |     | $\Delta t_{DS}$                 | $\Delta t_{DH}$ | $\Delta t_{DS}$ | $\Delta t_{DH}$ | $\Delta t_{DS}$ | $\Delta t_{DH}$ | $\Delta t_{DS}$ | $\Delta t_{DH}$ | $\Delta t_{DS}$ | $\Delta t_{DH}$ | $\Delta t_{DS}$ | $\Delta t_{DH}$ | $\Delta t_{DS}$ | $\Delta t_{DH}$ | $\Delta t_{DS}$ | $\Delta t_{DH}$ | $\Delta t_{DS}$ | $\Delta t_{DH}$ |

| DQ Slew rate<br>V/ns | 2.0 | 125                             | 45              | 125             | 45              | 125             | 45              | -               | -               | -               | -               | -               | -               | -               | -               | -               | -               | -               | -               |

|                      | 1.5 | 83                              | 21              | 83              | 21              | 83              | 21              | 95              | 33              | -               | -               | -               | -               | -               | -               | -               | -               | -               | -               |

|                      | 1.0 | 0                               | 0               | 0               | 0               | 0               | 0               | 12              | 12              | 24              | 24              | -               | -               | -               | -               | -               | -               | -               | -               |

|                      | 0.9 | -                               | -               | -11             | -14             | -11             | -14             | 1               | -2              | 13              | 10              | 25              | 22              | -               | -               | -               | -               | -               | -               |

|                      | 0.8 | -                               | -               | -               | -               | -25             | -31             | -13             | -19             | -1              | -7              | 11              | 5               | 23              | 17              | -               | -               | -               | -               |

|                      | 0.7 | -                               | -               | -               | -               | -               | -               | -31             | -42             | -19             | -30             | -7              | -18             | 5               | -6              | 17              | 6               | -               | -               |

|                      | 0.6 | -                               | -               | -               | -               | -               | -               | -               | -               | -43             | -59             | -31             | -47             | -19             | -35             | -7              | -23             | 5               | -11             |

|                      | 0.5 | -                               | -               | -               | -               | -               | -               | -               | -               | -               | -74             | -89             | -62             | -77             | -50             | -65             | -38             | -53             | -               |

|                      | 0.4 | -                               | -               | -               | -               | -               | -               | -               | -               | -               | -               | -               | -127            | -140            | -115            | -128            | -103            | -116            | -               |

NOTE:

1. For all input signals the total  $t_{DS}$  (setup time) and  $t_{DH}$  (hold time) required is calculated by adding the datasheet value to the derating value listed in Table 11.

2. Setup ( $t_{DS}$ ) nominal slew rate for a rising signal is defined as the slew rate between the last crossing of  $V_{REF(dc)}$  and the first crossing of  $V_{IH}(ac)$ min. Setup ( $t_{DS}$ ) nominal slew rate for a falling signal is defined as the slew rate between the last crossing of  $V_{REF(dc)}$  and the first crossing of  $V_{IL}(ac)$ max. If the actual signal is always earlier than the nominal slew rate line between shaded ' $V_{REF(dc)}$  to ac region', use nominal slew rate for derating value (see Figure 13) If the actual signal is later than the nominal slew rate line anywhere between shaded ' $V_{REF(dc)}$  to ac region', the slew rate of a tangent line to the actual signal from the ac level to dc level is used for derating value (see Figure 14)

3. Hold ( $t_{DH}$ ) nominal slew rate for a rising signal is defined as the slew rate between the last crossing of  $V_{IL}(dc)$ max and the first crossing of  $V_{REF(dc)}$ . Hold ( $t_{DH}$ ) nominal slew rate for a falling signal is defined as the slew rate between the last crossing of  $V_{IH}(dc)$ min and the first crossing of  $V_{REF(dc)}$ . If the actual signal is always later than the nominal slew rate line between shaded 'dc level to  $V_{REF(dc)}$  region', use nominal slew rate for derating value (see Figure 15) If the actual signal is earlier than the nominal slew rate line anywhere between shaded 'dc to  $V_{REF(dc)}$  region', the slew rate of a tangent line to the actual signal from the dc level to  $V_{REF(dc)}$  level is used for derating value (see Figure 16)

4. Although for slow slew rates the total setup time might be negative (i.e. a valid input signal will not have reached  $V_{IH}/V_{IL}(ac)$  at the time of the rising clock transition) a valid input signal is still required to complete the transition and reach  $V_{IH}/V_{IL}(ac)$ .

5. For slew rates in between the values listed in Table 11, the derating values may be obtained by linear interpolation.

6. These values are typically not subject to production test. They are verified by design and characterization.

**Figure 13: Nominal Slew Rate for  $t_{DS}$**

NOTE1 DQS, DQS# signals must be monotonic between  $V_{il(dc)max}$  and  $V_{ih(dc)min}$ .

**Figure 14: Tangent Line for  $t_{DS}$**

NOTE1 DQS, DQS# signals must be monotonic between  $V_{il(dc)max}$  and  $V_{ih(dc)min}$ .

**Figure 15: Nominal Slew Rate for  $t_{DH}$**

NOTE1 DQS, DQS# signals must be monotonic between  $V_{il(dc)max}$  and  $V_{ih(dc)min}$ .

**Figure 16: Tangent Line for  $t_{DH}$**

NOTE1 DQS, DQS# signals must be monotonic between  $V_{il(dc)max}$  and  $V_{ih(dc)min}$ .

**Figure 17: AC Input Test Signal Waveform Command/Address pins**

**Figure 18: AC Input Test Signal Waveform for Data with DQS,DQS# (differential)**

**Figure 19: AC Input Test Signal Waveform for Data with DQS (single-ended)**

**Figure 20: AC Input Test Signal Waveform (differential)**

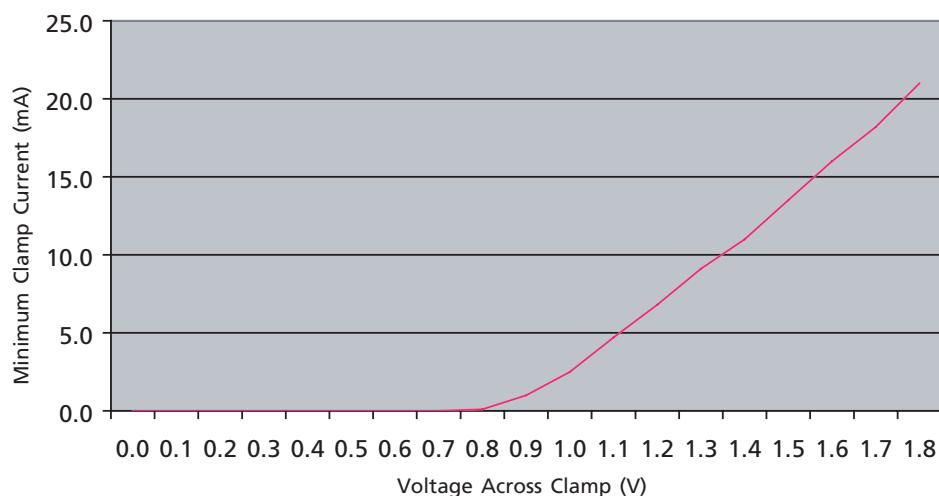

## Power and Ground Clamp Characteristics

Power and ground clamps are provided on the following input-only pins: BA1-BA0, A0-A12, CS#, RAS#, CAS#, WE#, ODT, and CKE.

**Table 12: Input Clamp Characteristics**

| Voltage Across Clamp (V) | Minimum Power Clamp Current (mA) | Minimum Ground Clamp Current (mA) |

|--------------------------|----------------------------------|-----------------------------------|

| 0.0                      | 0.0                              | 0.0                               |

| 0.1                      | 0.0                              | 0.0                               |

| 0.2                      | 0.0                              | 0.0                               |

| 0.3                      | 0.0                              | 0.0                               |

| 0.4                      | 0.0                              | 0.0                               |

| 0.5                      | 0.0                              | 0.0                               |

| 0.6                      | 0.0                              | 0.0                               |

| 0.7                      | 0.0                              | 0.0                               |

| 0.8                      | 0.1                              | 0.1                               |

| 0.9                      | 1.0                              | 1.0                               |

| 1.0                      | 2.5                              | 2.5                               |

| 1.1                      | 4.7                              | 4.7                               |

| 1.2                      | 6.8                              | 6.8                               |

| 1.3                      | 9.1                              | 9.1                               |

| 1.4                      | 11.0                             | 11.0                              |

| 1.5                      | 13.5                             | 13.5                              |

| 1.6                      | 16.0                             | 16.0                              |

| 1.7                      | 18.2                             | 18.2                              |

| 1.8                      | 21.0                             | 21.0                              |

**Figure 21: Input Clamp Characteristics**

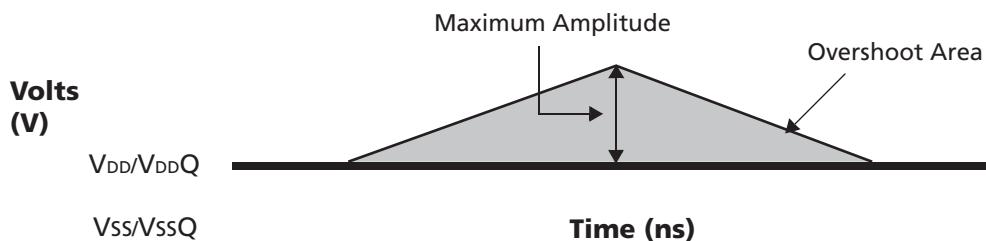

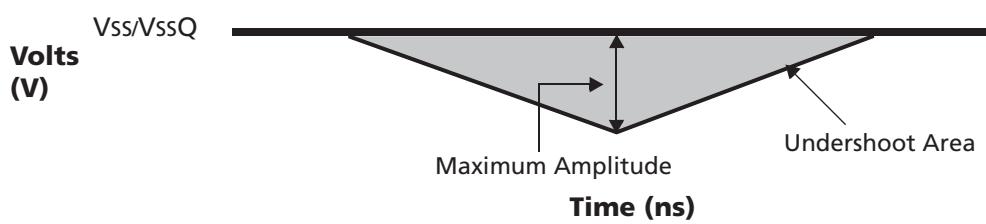

## AC Overshoot/Undershoot Specification

**Table 13: Address and Control Pins**

Applies to BA1-BA0, A0-A12, CS#, RAS#, CAS#, WE#, CKE, ODT

| Parameter                                                          | Specification |          |

|--------------------------------------------------------------------|---------------|----------|

|                                                                    | -3            | -37E     |

| Maximum peak amplitude allowed for overshoot area (See Figure 22)  | 0.9V          | 0.9V     |

| Maximum peak amplitude allowed for undershoot area (See Figure 23) | 0.9V          | 0.9V     |

| Maximum overshoot area above VDD (See Figure 22)                   | 0.75V-ns      | 0.56V-ns |

| Maximum undershoot area below Vss (See Figure 23)                  | 0.75V-ns      | 0.56V-ns |

**Table 14: Clock, Data, Strobe, and Mask Pins**

Applies to DQ0-DQxx, DQS, DQS#, RDQS, RDQS#, UDQS, UDQS#, LDQS, LDQS#, DM, UDM, LDM

| Parameter                                                          | Specification |          |

|--------------------------------------------------------------------|---------------|----------|

|                                                                    | -3            | -37E     |

| Maximum peak amplitude allowed for overshoot area (See Figure 22)  | 0.9V          | 0.9V     |

| Maximum peak amplitude allowed for undershoot area (See Figure 22) | 0.9V          | 0.9V     |

| Maximum overshoot area above VDDQ (See Figure 22)                  | 0.38V-ns      | 0.28V-ns |

| Maximum undershoot area below VssQ (See Figure 23)                 | 0.38V-ns      | 0.28V-ns |

**Figure 22: Overshoot**

**Figure 23: Undershoot**

## Output Electrical Characteristics and Operating Conditions

**Table 15: Differential AC Output Parameters**

| Parameter                           | Symbol       | Min                         | Max                         | Units | Notes |

|-------------------------------------|--------------|-----------------------------|-----------------------------|-------|-------|

| AC Differential Cross-Point Voltage | $V_{OX(AC)}$ | $0.50 \times V_{DDQ} - 125$ | $0.50 \times V_{DDQ} + 125$ | mV    | 1     |

| AC Differential Voltage Swing       | $V_{SWING}$  | 1.0                         |                             | mV    |       |

NOTE:

1. The typical value of  $V_{OX(AC)}$  is expected to be about  $0.5 \times V_{DDQ}$  of the transmitting device and  $V_{OX(AC)}$  is expected to track variations in  $V_{DDQ}$ .  $V_{OX(AC)}$  indicates the voltage at which differential output signals must cross.

**Figure 24: Differential Output Signal Levels**

**Table 16: Output DC Current Drive**

| Parameter                        | Symbol | Value | Units | Notes |

|----------------------------------|--------|-------|-------|-------|

| Output Minimum Source DC Current | IOH    | -13.4 | mA    | 1,3,4 |

| Output Minimum Sink DC Current   | IOL    | 13.4  | mA    | 2,3,4 |

NOTE:

1. For  $IOH$  (DC);  $VDDQ = 1.7V$ ,  $VOUT = 1420mV$ .  $(VOUT - VDDQ)/IOH$  must be less than  $21\Omega$  for values of  $VOUT$  between  $VDDQ$  and  $VDDQ - 280mV$ .

2. For  $IOL$  (DC);  $VDDQ = 1.7V$ ,  $VOUT = 280mV$ .  $VOUT/IOL$  must be less than  $21\Omega$  for values of  $VOUT$  between  $0V$  and  $280mV$ .

3. The DC value of  $VREF$  applied to the receiving device is set to  $VTT$ .

4. The values of  $IOH$  (DC) and  $IOL$  (DC) are based on the conditions given in Notes 1 and 2. They are used to test device drive current capability to ensure  $VIH$  (MIN) plus a noise margin and  $VIL$  (MAX) minus a noise margin are delivered to an  $SSTL\_18$  receiver. The actual current values are derived by shifting the desired driver operating point (See output IV curves) along a  $21\Omega$  load line to define a convenient driver current for measurement.

**Table 17: Output Characteristics**

| Parameter                      | Symbol | Min  | Nom | Max  | Units      | Notes |

|--------------------------------|--------|------|-----|------|------------|-------|

| Output impedance               |        | 12.6 | 18  | 23.4 | $\Omega s$ | 1,2   |

| Pull-up and Pull-down mismatch |        | 0    |     | 4    | $\Omega s$ | 1,2,3 |

| Output slew rate               |        | 1.5  |     | 5    | V/ns       | 1,4,5 |

NOTE:

1. Absolute specifications:  $0^{\circ}C \leq T_{case} \leq +85^{\circ}C$ ;  $VDDQ = +1.8V \pm 0.1V$ ,  $VDD = +1.8V \pm 0.1V$ .

2. Impedance measurement condition for output source DC current:  $VDDQ = 1.7V$ ;  $VOUT = 1420mV$ ;  $(VOUT - VDDQ)/IOH$  must be less than  $23.4\Omega$  for values of  $VOUT$  between  $VDDQ$  and  $VDDQ - 280mV$ . Impedance measurement condition for output sink DC current:  $VDDQ = 1.7V$ ;  $VOUT = 280mV$ ;  $VOUT/IOL$  must be less than  $23.4\Omega$  for values of  $VOUT$  between  $0V$  and  $280mV$ .

3. Mismatch is absolute value between pull-up and pull-down, both are measured at same temperature and voltage.

4. Output slew rate for falling and rising edges is measured between  $VTT - 250mV$  and  $VTT + 250mV$  for single ended signals. For differential signals (e.g. DQS - DQS#) output slew rate is measured between  $DQS - DQS\# = -500mV$  and  $DQS\# - DQS = +500mV$ . Output slew rate is guaranteed by design, but is not necessarily tested on each device.

5. The absolute value of the slew rate as measured from  $VIL$  (DC)MAX to  $VIH$  (DC) MIN is equal to or greater than the slew rate as measured from  $VIL$  (AC) MAX to  $VIH$  (AC) MIN. This is guaranteed by design and characterization.

**Figure 25: Output Slew Rate Load**

**Full Strength Pull-Down Driver Characteristics**

**Figure 26: Full Strength Pull-Down Characteristics**

**Table 18: Pulldown Current (mA)**

| Voltage (V) | Minimum | Nominal | Maximum |

|-------------|---------|---------|---------|

| 0.0         | 0.00    | 0.00    | 0.00    |

| 0.1         | 4.3     | 5.63    | 7.95    |

| 0.2         | 8.6     | 11.3    | 15.90   |

| 0.3         | 12.9    | 16.52   | 23.85   |

| 0.4         | 16.9    | 22.19   | 31.80   |

| 0.5         | 20.4    | 27.59   | 39.75   |

| 0.6         | 23.28   | 32.39   | 47.70   |

| 0.7         | 25.44   | 36.45   | 55.55   |

| 0.8         | 26.79   | 40.38   | 62.95   |

| 0.9         | 27.67   | 44.01   | 69.55   |

| 1.0         | 28.38   | 47.01   | 75.35   |

| 1.1         | 28.96   | 49.63   | 80.35   |

| 1.2         | 29.46   | 51.71   | 84.55   |

| 1.3         | 29.90   | 53.32   | 87.95   |

| 1.4         | 30.29   | 54.9    | 90.70   |

| 1.5         | 30.65   | 56.03   | 93.00   |

| 1.6         | 30.98   | 57.07   | 95.05   |

| 1.7         | 31.31   | 58.16   | 97.05   |

| 1.8         | 31.64   | 59.27   | 99.05   |

| 1.9         | 31.96   | 60.35   | 101.05  |

## Full Strength Pull-Up Driver Characteristics

**Figure 27: Full Strength Pull-up Characteristics**

**Table 19: Pull-Up Current (mA)**

| Voltage (V) | Minimum | Nominal | Maximum |

|-------------|---------|---------|---------|

| 0.0         | 0.00    | 0.00    | -0.00   |

| 0.1         | -4.3    | -5.63   | -7.95   |

| 0.2         | -8.6    | -11.3   | -15.90  |

| 0.3         | -12.9   | -16.52  | -23.85  |

| 0.4         | -16.9   | -22.19  | -31.80  |

| 0.5         | -20.4   | -27.59  | -39.75  |

| 0.6         | -23.28  | -32.39  | -47.70  |

| 0.7         | -25.44  | -36.45  | -55.55  |

| 0.8         | -26.79  | -40.38  | -62.95  |

| 0.9         | -27.67  | -44.01  | -69.55  |

| 1.0         | -28.38  | -47.01  | -75.35  |

| 1.1         | -28.96  | -49.63  | -80.35  |

| 1.2         | -29.46  | -51.71  | -84.55  |

| 1.3         | -29.90  | -53.32  | -87.95  |

| 1.4         | -30.29  | -54.90  | -90.70  |

| 1.5         | -30.65  | -56.03  | -93.00  |

| 1.6         | -30.98  | -57.07  | -95.05  |

| 1.7         | -31.31  | -58.16  | -97.05  |

| 1.8         | -31.64  | -59.27  | -99.05  |

| 1.9         | -31.96  | -60.35  | -101.05 |

## FBGA Package Capacitance

**Table 20: Input Capacitance**

| Parameter                                                                | Symbol | Min | Max  | Units | Notes |

|--------------------------------------------------------------------------|--------|-----|------|-------|-------|

| Input Capacitance: CK, CK#                                               | CCK    | 1.0 | 2.0  | pF    | 1     |

| Delta Input Capacitance: CK, CK#                                         | CDCK   | –   | 0.25 | pF    | 2     |

| Input Capacitance: BA1-BA0, A0-A12, CS#, RAS#, CAS#, WE#, CKE, ODT       | CI     | 1.0 | 2.0  | pF    | 1     |

| Delta Input Capacitance: BA1-BA0, A0-A12, CS#, RAS#, CAS#, WE#, CKE, ODT | CDI    | –   | 0.25 | pF    | 2     |

| Input/Output Capacitance: DQs, DQS, DM, NF                               | CIO    | 2.5 | 4.0  | pF    | 1     |

| Delta Input/Output Capacitance: DQs, DQS, DM, NF                         | CDIO   | –   | 0.5  | pF    | 3     |

NOTE:

1. This parameter is sampled.  $V_{DD} = +1.8V \pm 0.1V$ ,  $V_{DDQ} = +1.8V \pm 0.1V$ ,  $V_{REF} = V_{SS}$ ,  $f = 100$  MHz,  $T_{CASE} = 25^\circ C$ ,  $V_{OUT} (DC) = V_{DDQ}/2$ ,  $V_{OUT}$  (peak to peak) = 0.1V. DM input is grouped with I/O pins, reflecting the fact that they are matched in loading.

2. The input capacitance per pin group will not differ by more than this maximum amount for any given device.

3. The I/O capacitance per DQS and DQ byte/group will not differ by more than this maximum amount for any given device.

## IDD Specifications and Conditions

**Table 21: DDR2 IDD Specifications and Conditions**

Notes: 1-5; notes appear on page 33.

| Parameter/Condition                                                                                                                                                                                                                                                                                                                                                                                  | Symbol | Config                        | -3  | -37E | Units |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------------|-----|------|-------|

| <b>Operating one bank active-precharge current;</b><br>$t_{CK} = t_{CK}(\text{IDD})$ , $t_{RC} = t_{RC}(\text{IDD})$ , $t_{RAS} = t_{RAS \text{ MIN}}(\text{IDD})$ ; CKE is HIGH, CS# is HIGH between valid commands; Address bus inputs are SWITCHING; Data bus inputs are SWITCHING.                                                                                                               | IDD0   | x4, x8                        | TBD | 80   | mA    |